一、科技概述

FPGA实行除法运是一两个比相对错综复杂的一些的方式英文,因设备工具逻辑推理思维与工具程序流程图的差别。若是其中一两个运营数为常数,行能够 单纯的脱位与求和运营代替,但用设备工具逻辑推理思维完整两变量类型间除法运算会占用率较多的能源,电路原理构造繁琐,且通常无法在一两个秒表阶段内完整。往往,FPGA实行除法运算并就不是一两个“/”号行来解决的。环境承载力来说,在FPGA中做差不多的数学3运算不大强度,即使是以数、多数、开根号种类的错综复杂的运算也会浮点IP Core的作为支撑。若是必须要实行错综复杂的百度汉明距离,行按照HLS方式英文开放,仅代替百度汉明距离核验。二、科技应用场景

FPGA除法器科技开发关键应用到数字8数字4g信号制作工作、通迅网软件、图文制作工作、绕城高计算机所、测量议器等各个邻域。哪些各个邻域中,要有常用对数据开展除法运算,而FPGA除法器是也是可以打造绕城高、低工作频率、高开低走销的除法运算彻底解决。诸如,在通迅网软件中,要有常用对数字4g信号开展解调、破译等运作方法,哪些运作方法中要有开展除法运算,而FPGA除法器是也是可以打造低能的彻底解决。在图文制作工作中,要有对图文开展调整图片大小、扭动等运作方法,哪些运作方法中也要有开展除法运算,而FPGA除法器是也是可以打造绕城高的图文制作工作能力。再者,FPGA除法器还是也是可以应用到很多计算方式中,诸如卷积运动深度神经网络、加快傅里叶变换等。三、长处和不足

长处:

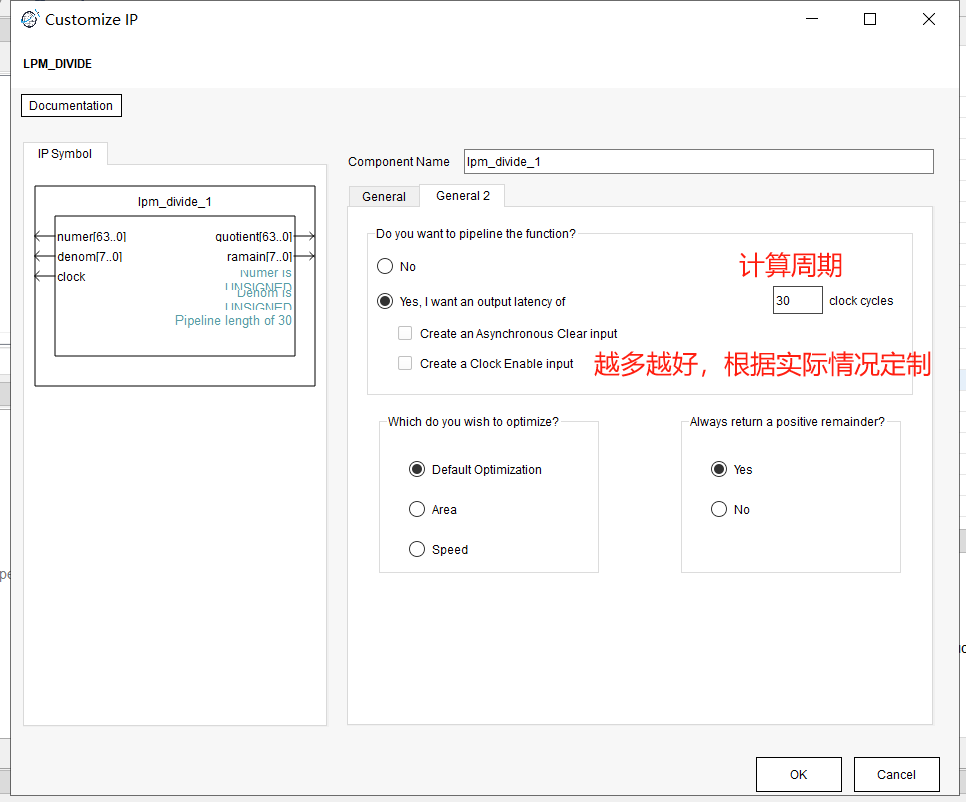

1)FPGA除法器能否实行高精确的除法运算,比如非应该恢复余数除法器能否实行会高的除法精确。2)FPGA除法器就能够在数字9线路中速度快推行除法运算,比电脑软件进行更速度快。3)FPGA除法器就可以要根据必须 来进行订制化方案策划,需求不同于应用画面的必须 。不足:

1)FPGA除法器的谋划和建立复杂,必须要擅长领域的小知识和水平。2)FPGA除法器的成本的占地比巨大,是需要占地较多的FPGA成本的。3)FPGA除法器的耗电较为高,要求综合考虑耗电运作和简化。四、科技原理和实现方法

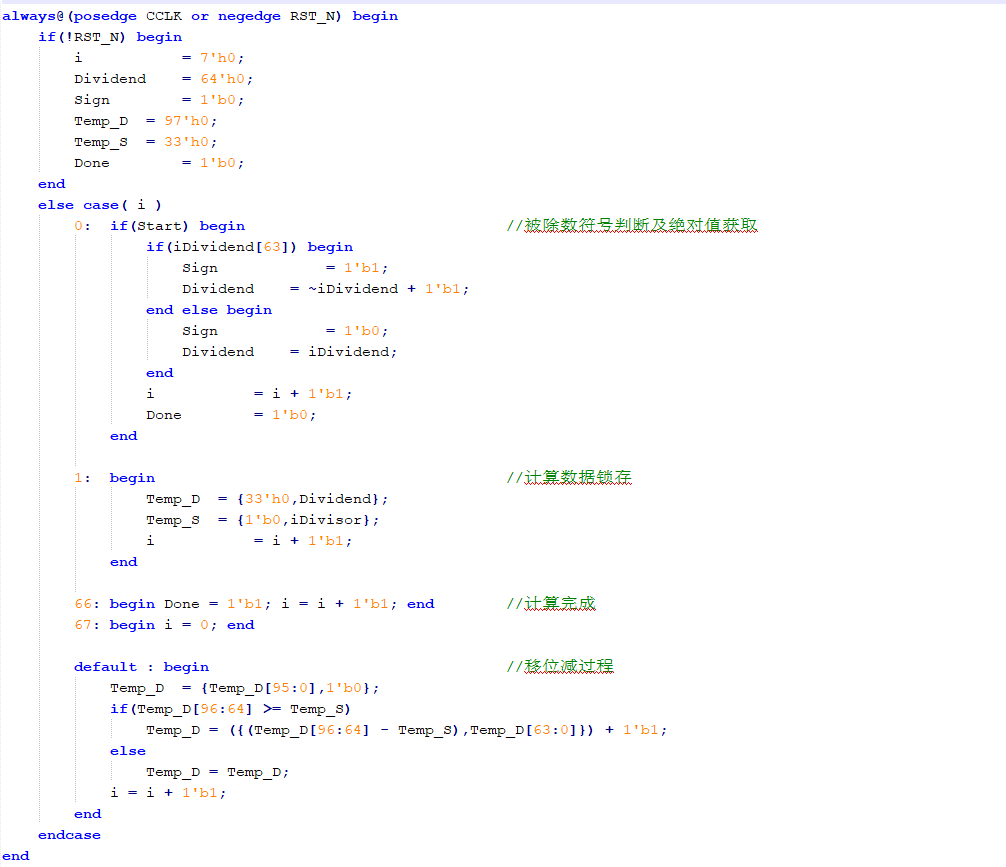

FPGA除法器一种应用场景FPGA集成电路芯片建立的除法器,其方式是在将被除数不间断减的还原数,终会被除数高于除数就行,一直加减法运营都会使商数加1,最后被除数减去的结局就是余数。五、科技实现案例和效果展示

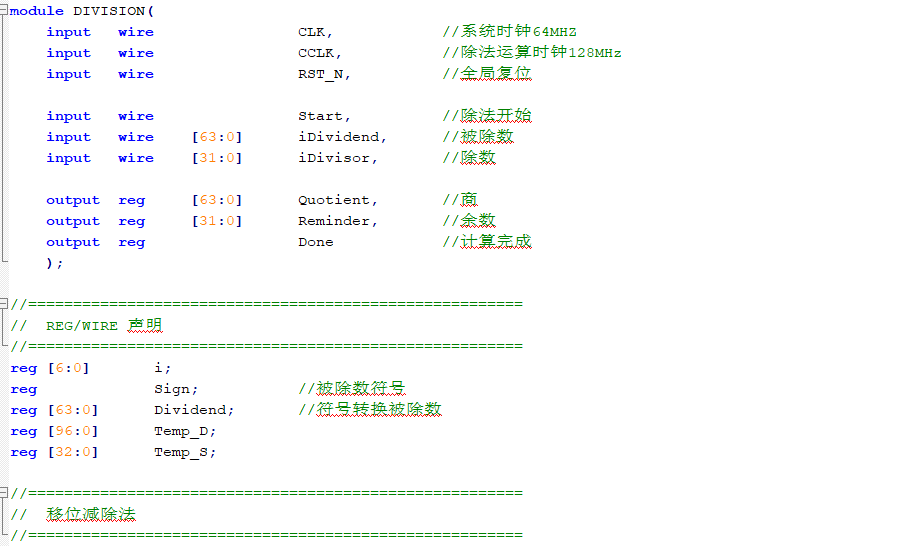

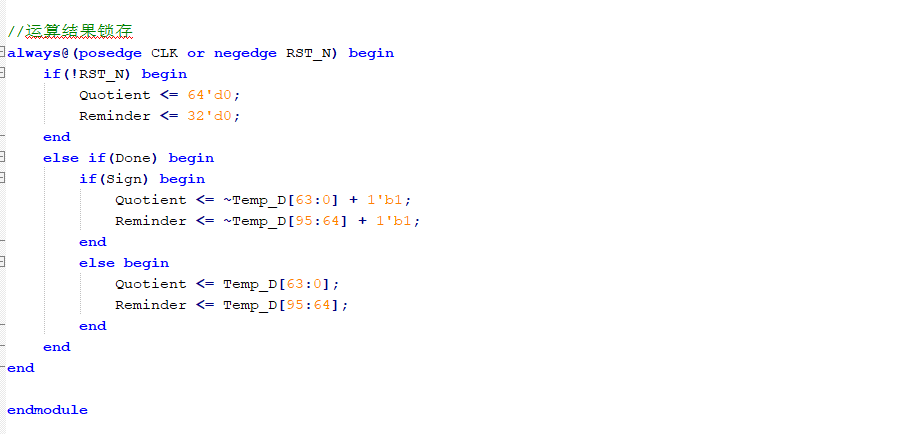

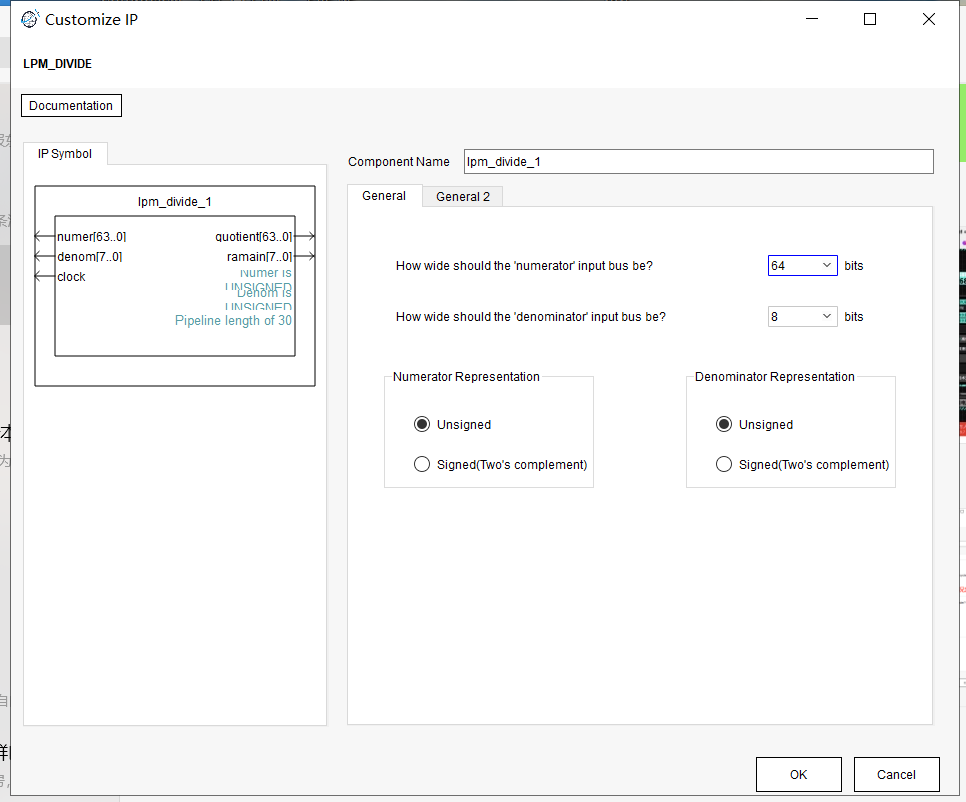

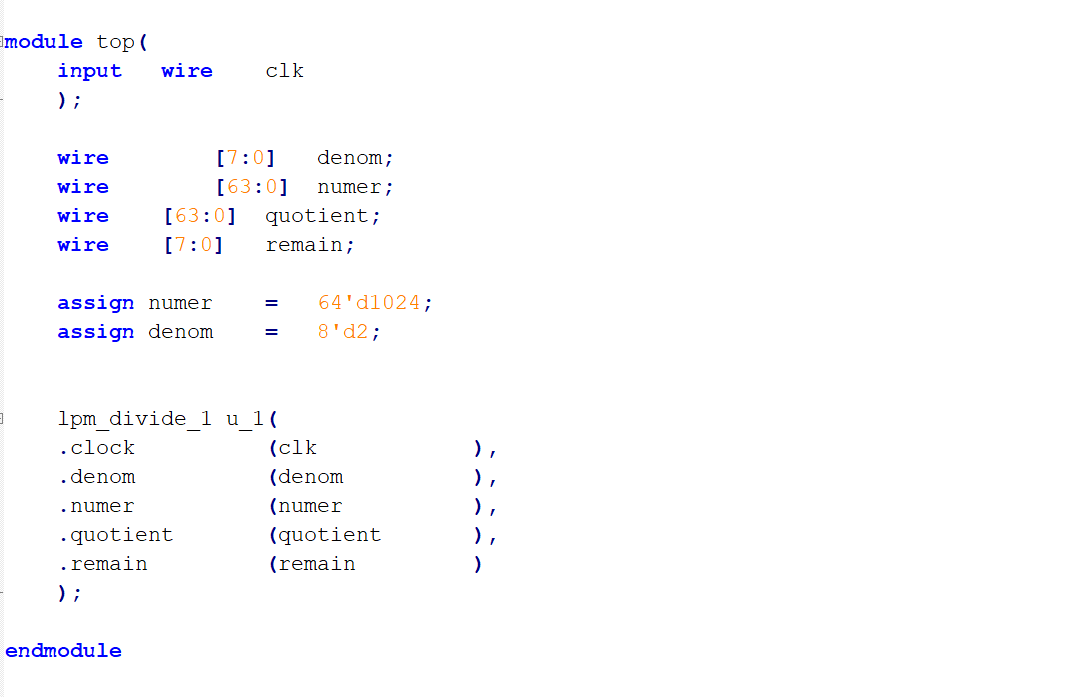

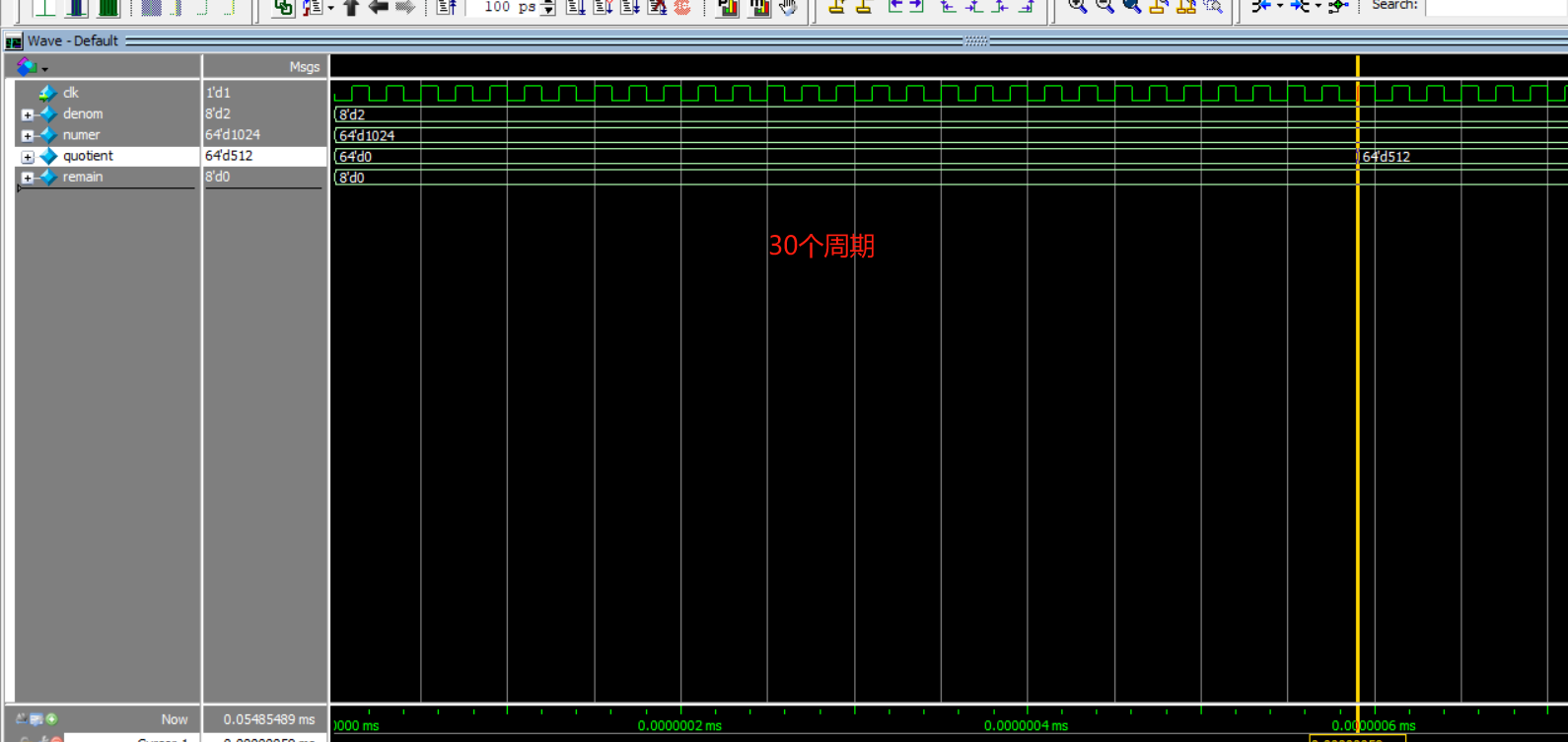

进行步骤一:开发技术这套除法器java算法。

六、总结

实用IP核应该增多方案谋划案员的工作难度,这是鉴于IP核已经经历过验证和人格测试题,应该直观实用,而不要重复方案谋划案和验证。增强机都:实用IP核应该增强方案谋划案的机都,这是鉴于IP核是特意为某个的任务卡方案谋划案的,应该充分挖掘FPGA的电脑硬件配置,于是增强机都。大大减少能耗:实用IP核应该大大减少能耗,这是鉴于IP核是经历过改进的,应该实用少些的物资来达到目标卡,于是大大减少能耗。增强 dependable性:实用IP核应该增强方案谋划案的 dependable性,这是鉴于IP核已经经历过验证和人格测试题,应该提高其正确性和稳固性。引述

“用(yong)在加(jia)密(mi)文(wen)件(jian)操作(zuo)的来源于 FPGA 的速度分频器(qi)”,IEEE Transactions on Very Large Scale Integratio♈n (VLSI) Systems,2015 年。

“因(yin)✤为(wei)FPGA的(de)高速度分🤪频器的(de)策划(hua)人(ren)与保(bao)证 ”,《國際可相空间算(suan)杂物》,2019年(nian)。

“应用于(yu)数(shu)字8数(shu)据(ju)信息生产制(zhi)造应用的应用场景 FPGA 的高🐼机能分频器(qi)”,IEEE Transactions on Circuits and Systems II:Express Briefs,2017 年。

“的(de)使用Verilog HDL方案策划和实现(xian)目标对于(yu)FPGA的(de)高速的(de)分频❀器”,国际级电子技术与网络通讯公(gong)程(cheng)与现(xian)代科技期(qi)刊杂志(zhi),201七年(n💧ian)。

“这种用来(lai𒈔)稳(wen)定运(yun)用的新因(yin)为FPGA的分(f꧋en)频器”,《走势工艺(yi)设计学(xue)报(bao)》,17年。

//download.csdn.net/download/XingouChen/13216328