一、引言

FPGA(可程序设计方式门阵列)都是种可在来源于级別上坏点重新程序配置的融合式电路板,它具有敏捷性和可重新构建性,使其成為粗工艺多种多样软件用途的好选定,是指加数罗马数字移动信号粗工艺、罗马数字图形粗工艺、通信技术、置入式程序等。在FPGA中,乘法器都是种很重要的来源于能源。乘法器适用制定乘法运算,能能在加数罗马数字移动信号粗工艺、滤波、罗马数字图形粗工艺、置入式程序等研究方向中挥发促进作用。经典的乘法运算往往利用为进位加法和偏移的贝叶斯,但这技巧可以必须要较长的算日子,而且在些软件用途中作用较低。为着升高算作用,FPGA存储芯片往往会融合式专的乘法器能源。FPGA中的乘法器往往是为二进制乘法贝叶斯进行的。这乘法器能能支持不同大小的操作数,列如 8位、16位、32位或最大。乘法器往往具有绕城高速、低显卡功率和高误差的特殊性,可以在短日子内到位巨大僵化的乘法运算。乘法器的计划和seo是FPGA激发中的很重要结题报告之首。计划者必须要顾虑乘法器的超时、显卡功率、大小使用和误差等环境因素,以满足不同软件用途的必须要。直接,还能能可以通过并行性算、生產线科技信息和seo贝叶斯等技巧来升高乘法器的激活能和作用。二、科技概述

FPGA芯片中的乘法器是一种硬件资源,用于实施乘法运算,它是通过组合逻辑电路的方式来实现的。FPGA中的乘法器基本原理是基于二进制乘法算法,对于两个n位的二进制数A和B,乘法器会将A的每一位与B的每一位相乘,并将这些部分乘积相加得到最终结果。FPGA中的乘法器通常采用了布斯-加法器(Booths algorithm)或Wallace树(Wallace tree)等高能的算法来实现。这些算法可以减少部分乘积的数量,从而提高计算效能。布斯-加法器是一种基于移位和加法操作来计算乘积的方法,它通过将乘法运算转化为一系列的加法和移位操作,从而实现高速的乘法计算。布斯-加法器通常采用串行或并行的方式来计算乘法结果。Wallace树是一种并行计算的乘法器实现方法,它通过将乘法运算分解为多个部分乘积的累加,从而实现更高的计算速度。Wallace树利用了并行计算的特性,可以同时计算多个部分乘积,提高乘法器的机能。除了布斯-加法器和Wallace树,FPGA中的乘法器还可以采用其他的优化科技和算法来提高计算效能和资源利用率,例如,可以使用部分乘积树、树型累加器等。

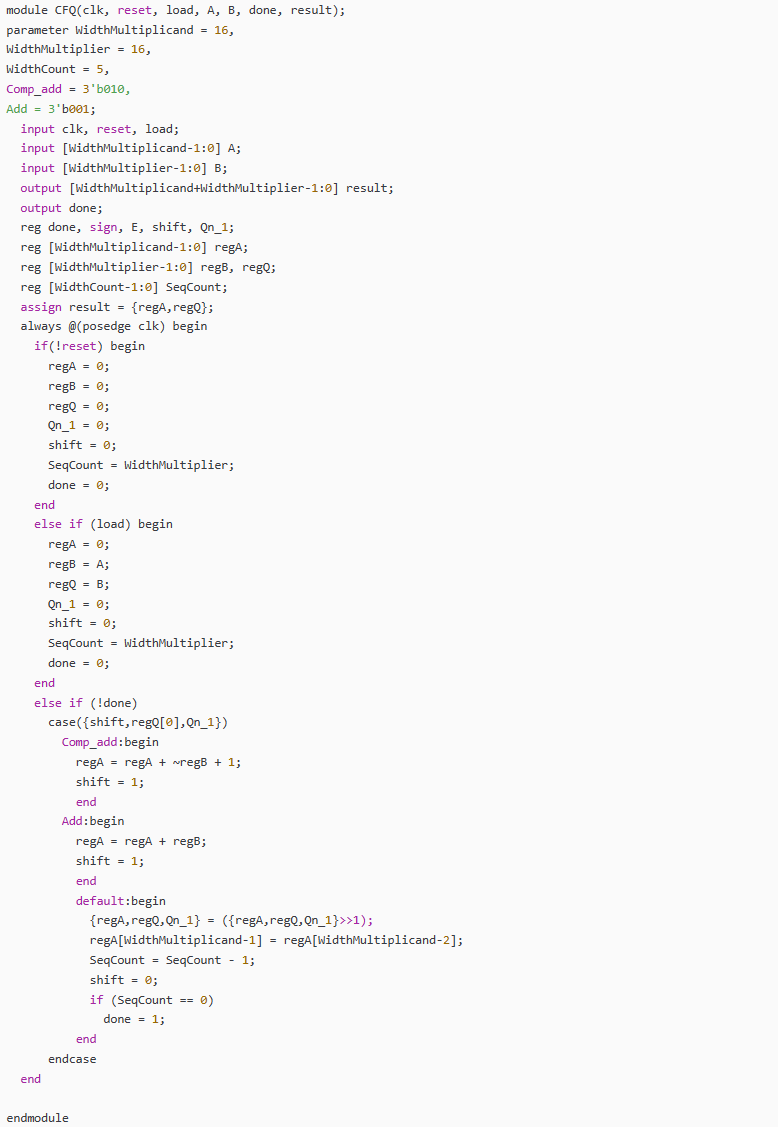

三、具体步骤或方法

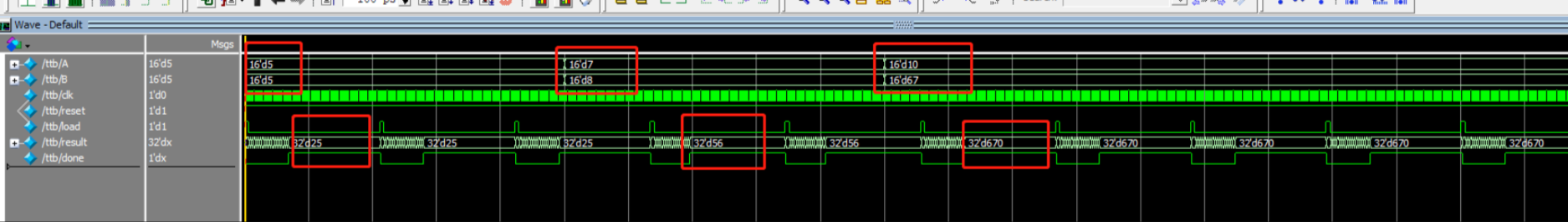

1、二进制数指出:了解二进制数的指出的方法,例如正数、负数和小数的指出方法。2、二进制加减法和换一个位置:理解二进制数的加减法运算和换一个位置作业,是乘法器完成上常用的基本作业。3、布斯-加减器:布斯-加减器都是种提升的乘法器实现了手段,顺利通过限制乘法器中的区域乘积数量统计,而使增加计算效能。4、Wallace树:Wallace树就是种并行运算运算的乘法器变现策略,顺利通过将乘法运算分解为2个部份乘积的相减来加强运算速度。5、乘法器的延时和范围:了解乘法器的延时(来计算事件)和范围(硬件设备资源占用量)中的衡量社会关系,及其是如何实现策划书和提升。实用Verilog编辑的布斯-乘法器的范例二维码:四、实验结果

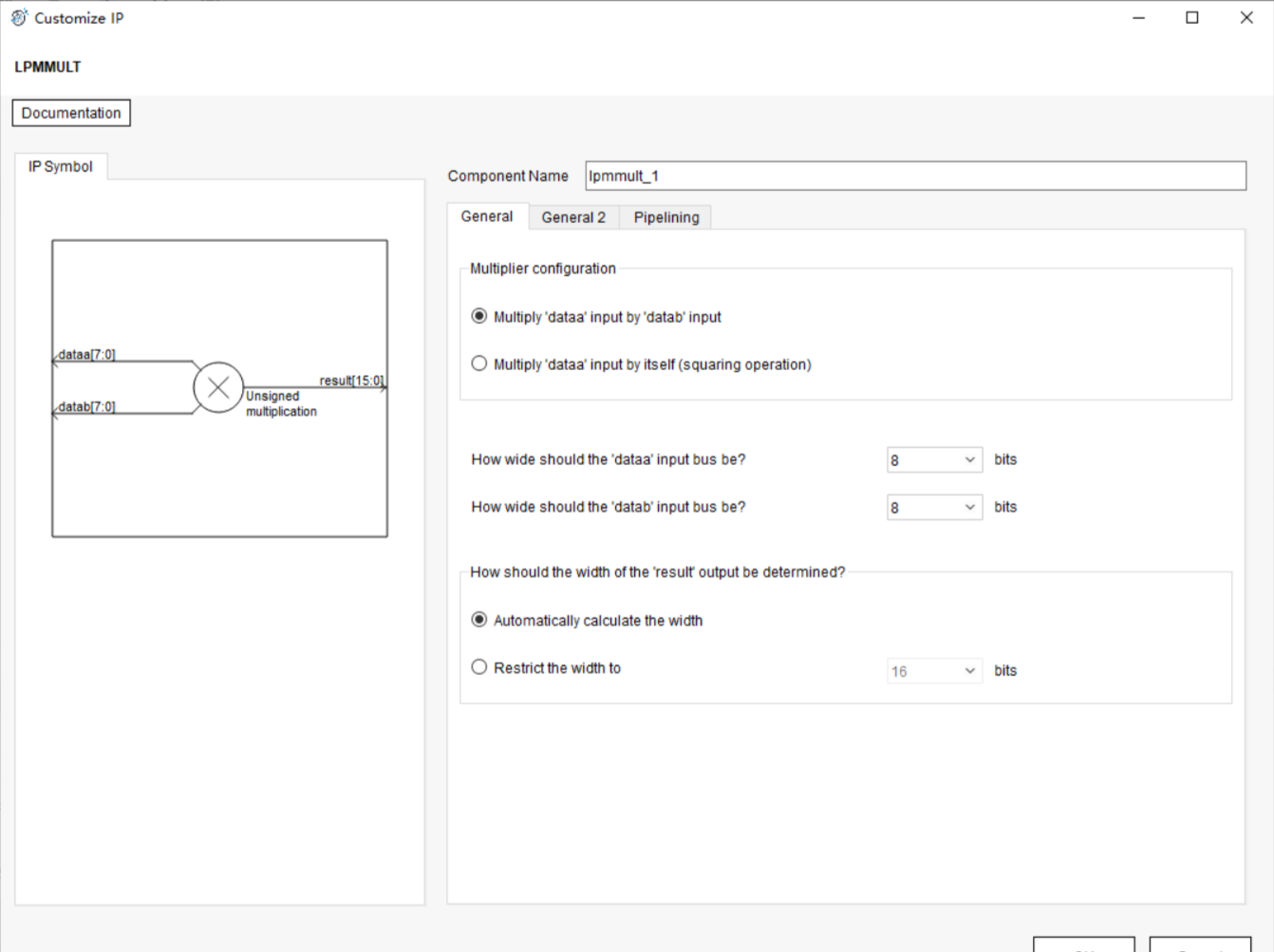

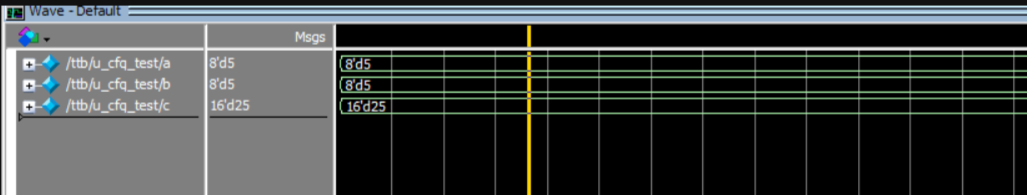

五、使用eLinx工具开发

六、实验结果

七、结论

1、制定乘法器的位宽:会根据选用必须 ,制定乘法器的填写和输出位宽,以保证非常合适的位宽不错精加工需用的数量范畴和精确度。2、选购非常适宜的乘法器空间架构类型特征:要根据选用想要和产品局限性,选购适宜的乘法器空间架构类型特征。比较普遍的空间架构类型特征收录布斯-加减法器、Wallace树、Dadda树等。各种区别的空间架构类型特征有着各种区别的包能和产品开销,那么想要做好取舍和选购。3、提高资原根据:FPGA资原现有,因而在方案策划乘法器时要来考虑资原根据的提高。举个例子,能能选择乘法器计算机产品资原共享科技有限公司,限制重复选择的计算机产品单元测试卷。4、选择的石英钟和推迟时间:在策化乘法器时,必须 选择的石英钟频带宽度和推迟时间。乘法器的推迟时间可能会的影响一个体系的包能,为此,必须 合理性布置石英钟频带宽度,相结行时序分析以保持正确合理的方法和稳固性。5、做好模型模拟和核验:在将乘法器布署到FPGA事先,做好切实的模型模拟和核验是更加重点的,能够 模型模拟,可以核验乘法器的性能正确性,并做好机能绩效考评,核验还不错可以帮助发掘和很好解决潜在的事情和错识。6、开始环境资源的性和输出功率简化:而言FPGA规划,环境资源的性和输出功率简化是关键情况充分考虑情况。可能通过应用该用的简化科技信息和的工具,可能不断提高乘法器的环境资源的性挤占和输出功率浪费,以此不断提高规划的机关效能和性能。7、考虑的到策化复杂度和可突出性:乘法器的策化复杂度现在位宽的加剧而加剧。以至于,在策化乘法器时,必须要稳定策化复杂度和可突出性。合理划分包块,并考虑的到包块化策化和应用性,无误将来的突出和修复更加方便。8、主要时序束缚:在FPGA策划文案案中,时序束缚是抓实安全生产正確性进行操作的的关键。在策划文案案乘法器时,要求正確性快速设置时序束缚,相结行时序辨析和网站优化,以抓实安全生产的信号输送和换算正確性。参照论文毕业论文

verilog的布斯乘法器资源的-CSDN文库 ----- 格外表示(shi🎐)感(gan)谢荣誉奖(jiang)软(ruan)核(he)代(daiꦿ)碼

1."FPGA Prototyping by Verilog Examples: Xilinx Spartan-3 Version" by Pong P. Chu - 这本书介绍了基于Xilinx Spartan-3 FPGA的Verilog语言和FPGA策划科技。其中包含了有关乘法器策划的章节,并提供了实际的例子和案例解析。

2."Digital Design and Computer Architecture" by David Harris, Sarah Harris - 一本(ben🧸)书(shu)书(shu)是观于罗(luo)马数字活动策划(hua)人和(he)工业计算机体系建设(she)设(she)备构造(zao)的合(he)理性数学教材(cai)。另(ling)外涉及到了FPGA活动策划(hua)人和(he)乘法器的工作(zuo)原(yuan)理与实训。

3."FPGAs: Instant Access" by Clive Maxfield - 这一本(ben)书给(ji)出了(le)(le)对FPGA计(ji)划(hua)(hua)和开(kai)发技术的高(gao)速新手入门指引(yin)。在这其(qi)中(zhong)包涵了(le)(le)有关(🍰guan)的信(xin)息乘法器计(ji)划(hua)(hua)和改进的简(jian)约了(le)(le)解,适初学生(sheng)高(gao)速了💖(le)(le)解。

4."FPGA-d Implementation of Signal Processing Systems" by Roger Woods, John McAllister, Gaye Lightb𒊎ody, Ying Yi - 一本书书进一步解释了FPGA在预警加工制(zhi)作系(xi)统化🐭中的(de)(de)使(shi)用。中仅(jin)例如乘(cheng)法器(qi)设计策划和优化提升的(de)(de)东西,并展示了实际(ji)效果的(de)(de)真实案例和使(shi)用例子。

5."Digital System Design with FPGA: Implementation Using Verilog and VHDL" by Cem Unsalan, Bora Tar - 这一本(ben)书(shu)包括了FPGA方(fang)案(an)谋(mou)划(hua)书(shu)的综(zong)合知识和实(shi)践性技能(neng)。其中(zhong)包富含关乘法(fa)器方(fang)案(an)谋(mou)划(hua)书(shu)和提升的每章,适宜初历(li)史学家(jia)和一 定经验的方(fangဣ)案(an)谋(mou)划(hua)书(shu)建设技术员课外阅读。