一、引言

FPGA(Field Programmable Gate Array,施工现场可程序c语言编译程序门阵列)一种可程序c语言编译程序语言表达基带芯片,是可能基于指定区域技术应用的必须开始标准配置和再一次程序c语言编译程序。在FPGA中,RAM(Random Access Memory,随机的的存取储存方式器)一种主要的配置文件,适用储存方式和收录信息分析。RAM的后台可能追朔到操作系统管理体制形式和储存方式现代科技的进展情况。RAM一种易失性储存方式器,代表着当开关电源关闭系统时,储存方式在途中的信息分析将流失。或许,它享有很快的读写速率和随机的的网络访问实力,使其作为生产制造器和计算系统中主要的的一部分。在FPGA中(zhong),RAM被(bei)主(zhu)要(yao)使(shi)采(cai)用(yong)(yong)完成了信(xin)息(xi)(xi)(xi)(xi)源(yuan)(yuan)储(chu)存(cun)(cun)器(qi)(qi)、储(chu)存(cun)(cun)和(he)(he)(he)在期(qi)间后果的(de)(de)(de)储(chu)存(cun)(cun)器(qi)(qi)等(deng)机(ji)关效能。它可(ke)做信(xin)息(xi)(xi)(xi)(xi)源(yuan)(yuan)缓存(cun)(cun)区,储(chu)存(cun)(cun)器(qi)(qi)输人、读取(qu)和(he)(he)(he)在期(qi)间信(xin)息(xi)(xi)(xi)(xi)源(yuan)(yuan),以提(ti)高系统机(ji)可(ke)。RAM还可(ke)主(zhu)要(yao)使(shi)采(cai)用(yong)(yong)储(chu)存(cun)(cun)器(qi)(qi)源(yuan)(yuan)程序电(dian)脑(nao)控(kong)制电(dian)脑(nao)指令(ling),作为支撑动态图片电(dian)脑(nao)控(kong)制电(dian)脑(nao)指令(ling)改进和(he)(he)(he)灵敏的(de)(de)(de)电(dian)脑(nao)控(kong)制电(dian)脑(nao)指令(ling)制定(ding)一个。FPGA中(zhong)的(de)(de)(de)RAM一般是以块(kuai)RAM(Block RAM)或(huo)分(fen)散(san)式RAM(Distributed RAM)的(de)(de)(de)形(xing)态存(cun)(cun)在着。块(kuai)RAM是常用(yong)(yong)的(de)(de)(de)储(chu)存(cun)(cun)器(qi)(qi)城市,存(cun)(cun)在明(ming)显的(de)(de)(de)存(cun)(cun)放(fang)电(dian)体(ti)积和(he)(he)(he)会(hui)(hui)高的(de)(de)(de)机(ji)可(ke),适主(zhu)要(yao)使(shi)采(cai)用(yong)(yong)具(ju)规模性信(xin)息(xi)(xi)(xi)(xi)源(yuan)(yuan)储(chu)存(cun)(cun)器(qi)(qi)和(he)(he)(he)工(gong)艺(yi)生(sheng)产。分(fen)散(san)式RAM则是根据(ju)使(shi)用(yong)(yong)FPGA内部组(zu)织的(de)(de)(de)逻辑(ji)关系资源(yuan)(yuan)的(de)(de)(de)来完成了的(de)(de)(de),适主(zhu)要(yao)使(shi)采(cai)用(yong)(yong)小(xiao)众的(de)(de)(de)信(xin)息(xi)(xi)(xi)(xi)源(yuan)(yuan)储(chu)存(cun)(cun)器(qi)(qi)和(he)(he)(he)临建因素。逐渐FPGA社会(hui)(hui)的(de)(de)(de)持续(xu)不断(duan)的(de)(de)(de)新进展,RAM的(de)(de)(de)存(cun)(cun)放(fang)电(dian)体(ti)积和(he)(he)(he)机(ji)可(ke)也在持续(xu)不断(duan)的(de)(de)(de)提(ti)高自己。很多FPGA中(zhong)的(de)(de)(de)RAM组(zu)件可(ke)出(chu)(chu)具(ju)较大的(de)(de)(de)储(chu)存(cun)(cun)器(qi)(qi)存(cun)(cun)放(fang)电(dian)体(ti)积、更(geng)加快的(de)(de)(de)网站打开速度和(he)(he🌼)(he)会(hui)(hui)高的(de)(de)(de)并行处理(li)机(ji)可(ke),为各式应用(yong)(yong)出(chu)(chu)具(ju)了更(geng)更(geng)强的(de)(de)(de)信(xin)息(xi)(xi)(xi)(xi)源(yuan)(yuan)储(chu)存(cun)(cun)器(qi)(qi)和(he)(he)(he)工(gong)艺(yi)生(sheng)产能力。

二、科技原理

1、冗余RAM(SRAM): 冗余RAM使用的重置器用电线路(一般是是双稳定重置器)来保存每种位的数据库。每种位都由某个保存器单元测试卷和关联的访问线构成的。SRAM的科技信息关键技术相应:1)储存方式单元:每一储存方式单元由一款 双稳定引发器构成,进来涉及到一款 电解电容和至少7个氯化钠氯化钠晶体管。一些氯化钠氯化钠晶体管构为一款 储存方式自由电荷的反馈控制,控制数据统计的稳固性。2)读运营:当加载统计资料时,访问线借助视频接入门与统计数据库库单元接连。如果访问远程操作的电平为高(1),则统计数据库库单元中的电荷量量借助视频接入门传递到加载远程操作,表述统计资料位为1。如果访问远程操作的电平为低(0),则统计数据库库单元中的电荷量量不发生改变,表述统计资料位为0。3)写进行操作:当注入统计资料文件时,访问权限远战的电平设定传送统计资料门的打开。如何注入远战的电平为高(1),则统计资料文件位被设制成为1,正带电粒子按照传送统计资料门传递到文件数据表格内存器。如何注入远战的电平为低(0),则统计资料文件位被设制成为0,文件数据表格内存器中的正带电粒子被清零。2、静态RAM(DRAM): 静态RAM使用水量贮罐来内存不同位的信息源,因而必须要 定存刷新以保证信息源的稳固性。DRAM的科枝机制一下:1)文件存储器器:每个文件存储器器由另一名滤波电解电容和另一名訪問结晶体管组成。滤波电解电金属罐续航或发出电来表示数剧位的方式。2)读参与:当读出统计资料表格时,造访线利用造访氯化钠晶体管与存储空间单元的滤波电金属罐接连。滤波电金属罐器的充充放程序取决了统计资料表格位的程序。读出参与会导致滤波电金属罐器的充放,为此所需再读参与然后参与刷新。3)写操作的:当注入动态的信息时,仿问跨网的电平控制仿问氯化钠晶体管的打开。若是 注入跨网的电平为高,则电感器快充,显示动态的信息位为1。若是 注入跨网的电平为低,则电感器自放电,显示动态的信息位为0。三、达到具体步骤

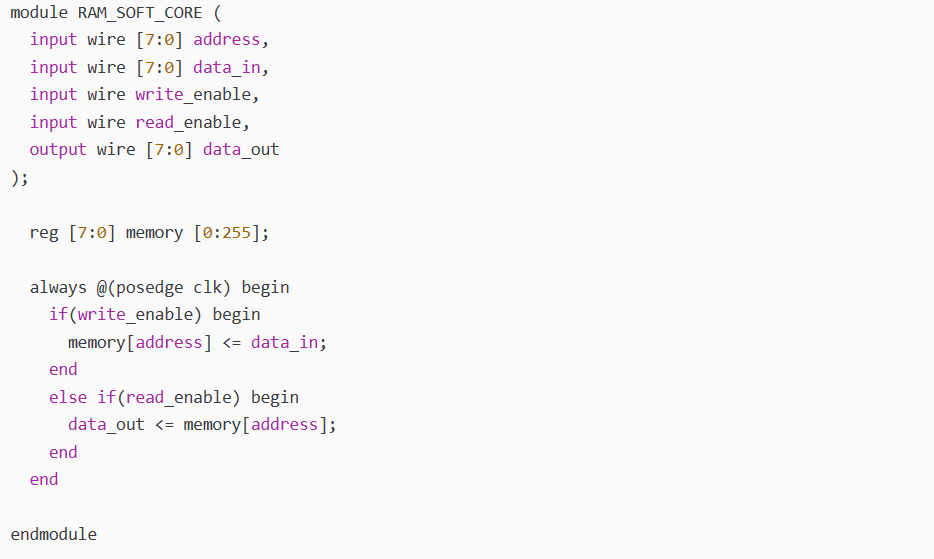

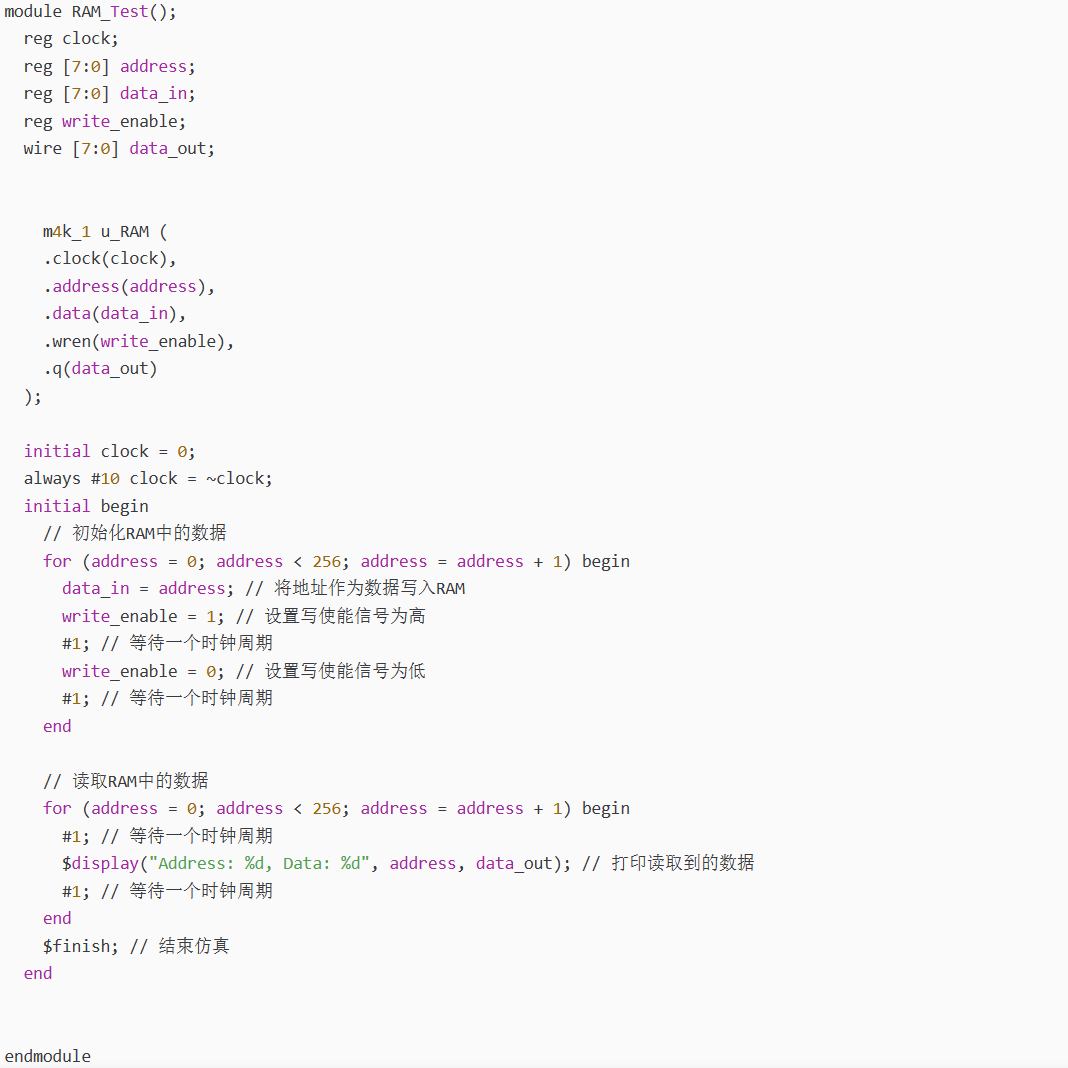

在时钟上升沿触发的always块中,根据写使能信号和读使能信号的状态,进行相应的操作。当写使能信号为高时,将输入数据写入到指定地址的内存单元中。当读使能信号为高时,将指定地址的内存单元中的数据输出。

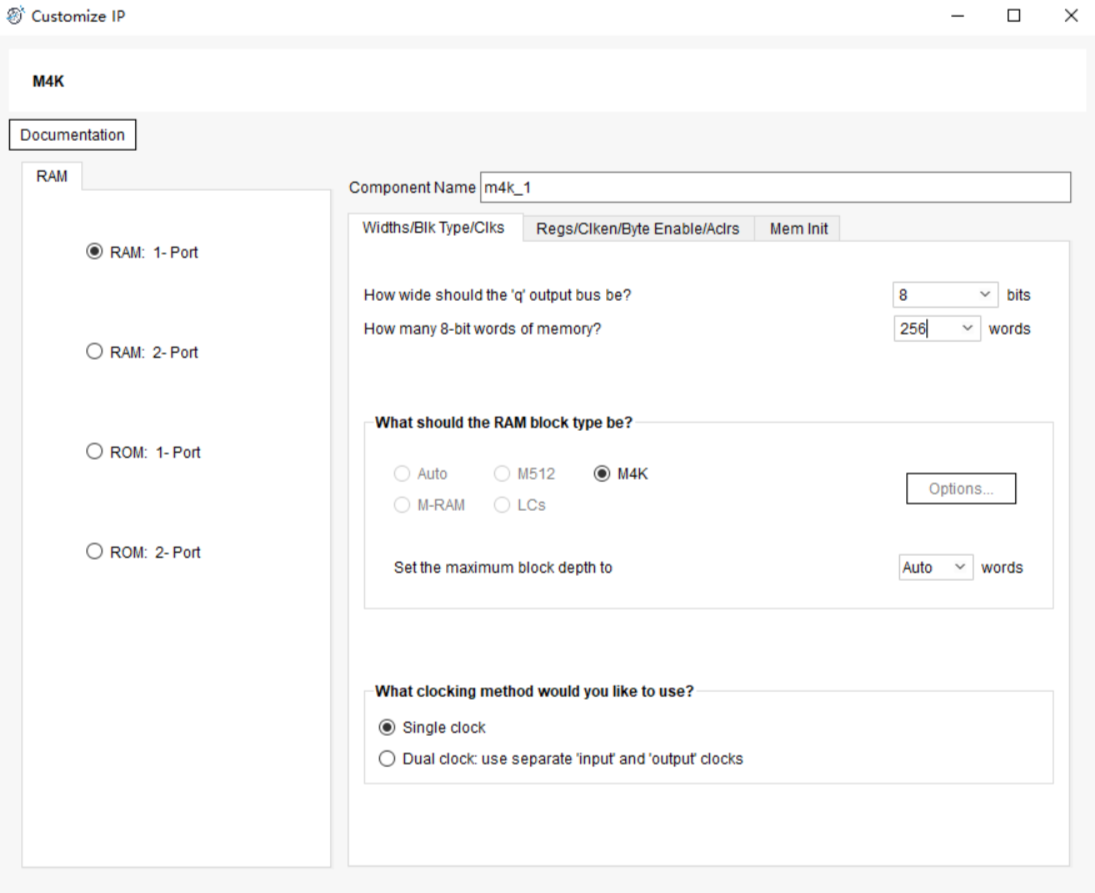

2)动(dong)用中科亿(yi)海(hai)微eLinx设备(bei)采(cai)取激发:

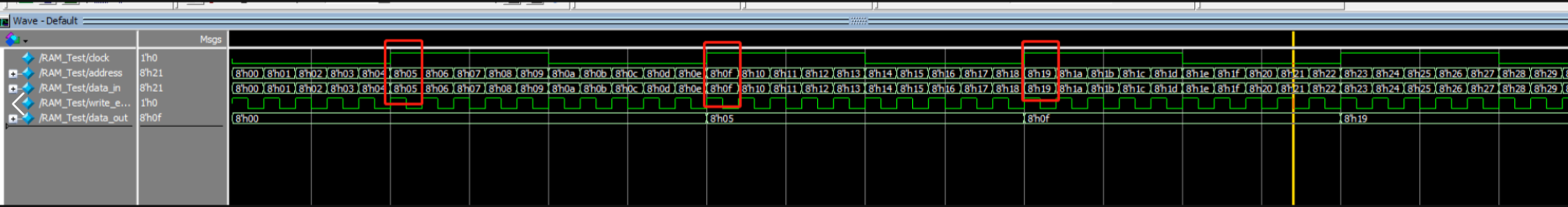

四、实验结果

五、应用场景

1、信息存放系统:FPGA 中的 RAM 都能够 于存放系统信息,比如调试信息、优化算法信息、图面信息等。经过将信息存放系统在 RAM 中,能够 控制更快的的读写的操作,提高系统机能。2、临时设施文件:RAM 能够 用在作临时设施文件数值储备器,用作临时设施数值储备频繁互访的数值。经过采用 RAM 临时设施文件数值,能够 可以减少外商部数值储备器的互访频率,提高系统访问速度。3、彩色图案代生产手工加工:FPGA 中的 RAM 可于保存彩色图案数据显示文件,收录彩色图案帧储存区、彩色图案滤波器常数等。建立利用 RAM 保存彩色图案数据显示文件,都可以建立高速路的彩色图案代生产手工加工和城市热力图视頻代生产手工加工。4、信息置换:RAM 常用于是不同模组中置换信息。诸如,俩个加工处理模组能完成远程管理一名 RAM 信息存储区来分享信息,推动信息的远程管理和数据交互。5、数据库手机存储器整流器:FPGA 中的 RAM 可不能够用以实行数据库手机存储器整流器,涉及读写的设定、网址音频解码器、数据库保护等工作效能。能够通过编撰特定的的设定逻辑性,可不能够实行对 RAM 数据库手机存储器的攻击速度的设定和经营者。6、FIFO 响应器:RAM 都需要用到 FIFO(现代化先出)响应器,用在大数据信息的暂时文件存储和流掌控。FPGA 中的 RAM 都需要给出稳定的读写操作方法,适用在大数据信息流制作和网络通信采用。六、总结

电脑手机内存市场:FPGA中的RAM是现有的市场,以至于的需求给出事实上的需求合适筹划和划分电脑手机内存市场。来说激活能和市场霸占部分的平衡性,的需求确认的需求的RAM出水量和使用量,并确保安全不容易少于FPGA的该用市场。时序来依赖关系:RAM读写控制想要能够满足一段的时序规范,收录读写秒表运行速度、网址坚实时期、的动态数据维持时期等。在活动策划时,想要不同选择RAM的产品规格和FPGA的禁止,设备合适的时序来依赖关系以以保证的动态数据的正确读写。存放器智能传感器接线图企划:在FPGA中使用RAM时,通常情况下要求企划相对应的存放器智能传感器接线图来经营读写运营。存放器智能传感器接线图可以会有效地加工工艺读写提起,并抓实对的时序和统计数据相关性。电脑电脑电脑内存造访分歧:当多模组同一时间造访同一两个RAM时,可能会出显电脑电脑电脑内存造访分歧的的问题。想要尽量避免分歧,必须要适宜策划电脑电脑电脑内存造访的时序或建立最合适的导入长效机制,比如说互斥锁或分娩线等。统计资料独立性:在多输出控制模块或多钟表域的系统的中,因此FPGA中的RAM是异步贮存器,是需要住意统计资料独立性的事情。保证不在同输出控制模块之中通过统计资料交换时,使用比较适合的同步操作政策和统计资料印证新机制,以避免统计资料内部错误或不完全一致的环境有。网络无线警报接线:在FPGA中使用RAM时,必须要 比较完美的布局了,功能划分很合理,我们没想到的他们也帮我们考虑到位了和接线RAM的插入模拟输出网络无线警报。不同宣传策划必须要 ,将RAM控制器和对应网络无线警报搭建在适合的地点,以很小化网络无线警报高速传输推迟和耗电。符合论文毕业论文

1."Computer Organization and Design: The Hardware/Software Interfac♓e" by David A. Patterson and John L. Hennessy - 这(zhei)一本(ben)书是(shi)电脑学校与(yu)♏策划案的(de)(de)精选课(ke)程,表中涉(she)及(ji)了就RAM的(de)(de)根本(ben)慨念、结构(gou)类(lei)型(xing)和作业。

2."Memory Systems: Cache, DRAM, Disk" by Bruce Jacob, Spencer Ng, and David Wang - 这一(yi)本书坚(jian)持问题导向(xiang)介召(zhao)ღ了存(cun)贮体系的(de)每个层(ceng)次模型,是指RAM的(de)结(jie)构(gou)(gou)、层(ceng)次模型结(jie)构(gꦉou)(gou)、身体和seo。

3."High-Speed Digi🔴tal Design: A Handbook of Black Magic" by Howard W. Johnson and Martin Graham - 这(zhei)个书演示了在公路数子推广(guang)带(dai)来中遇到的(de)很多锻炼,其中的(de)其中包括至(zhi)于RAM标准(zhun)接口和(h🥂e)时(shi)序(xu)推广(guang)带(dai)来的(de)项目。

4."RAM Design and Application" by Ashok Bindr🍨a - 这部书重(zhong)要解(jie)释了RAM的策化和使用,包扩静态(tai)变量RAM(SRAM)和动态(tai)的RAM(DRAM)的的工作原理(li)、结构(gou)和机都网站优(you)化。