一、引言

FPGA(现厂可程序编写门阵列)不是种可程序编写逻辑关系电子器件,具有敏捷性和可相空间性,大量代替数码控制电路策化和嵌到式设备搭建。在FPGA中,FIFO(First-In, First-Out)不是种常见的随意调节器结构,代替没有人同的石英钟域之間采取数值统计互传和加载。FPGA中的FIFO一般 由双串口内存条构建,表中有其中的串口代替导出资料源硬盘数值统计,另有其中的串口代替读入数值统计。FIFO內部有有其中的读表针和有其中的写表针,代替指示箭头下有其中的要导出资料源硬盘或读入的方位。当数值统计被读入FIFO时,写表针的向前看转移;当数值统计被导出资料源硬盘时,读表针的向前看转移。这个,担保了高端先出的数值统计先后顺序。FIFO在FPGA中的广泛应用非常大量,特别是数值统计流工作、微波通信主板接口、高速的数值统计采集等领域行业。它可以解绝不同石英钟域之間的数值统计互传状况,一同还能展示 加载职能,表明数值统计互传可以以合适的车速采取,最后应对数值统计缺失或负载。FPGA供应商一般 展示 了各类型和大小的FIFO IP核(流体智力房子产权核),可以方便地结合到策化中。最后,FPGA搭建辅助手段也展示 了对应的策化辅助手段和资源性,以简易化FIFO的使用和设置。二、原理

1.内控存储空间空间器器:FIFO由一内控存储空间空间器器组成,一般 不是双服务器服务器端口处的存储空间空间器器。一服务器服务器端口处代替写入,大数据显示,另一服务器服务器端口处代替读出大数据显示。2.写游标和读游标:FIFO外部有两个人游标,一名是写游标,于显示灯标志下一名要读数据表格源的地理职位;另一名是读游标,于显示灯标志下一名要读数据表格源的地理职位。3.注入统计资料:当有新的统计资料要注入FIFO时,写游针会往前走中移动到下1个可以的部位,并将统计资料注入该部位。4.导出信息表格:当要求导出FIFO中的信息表格时,读结构体指针会不断往前中移动到下有一个要导出的选址,并将该选址的信息表格输出电压。5.比较好的先出:因此写指南和读指南的运动顺寻是固定不动的,FIFO能保证了写入,FIFO的数剧如果根据鸟卵的顺寻被载入,即比较好的先出。6.减慢和访问量把控好:FIFO展示 了临时设施的数据文件显示存储效能建设,行用在减慢的数据文件显示,以转变不而且钟域范围内的的数据文件显示高速传输数据传输数据速度的差异。它还行用在访问量把控好,当读入方和加载方的传输数据速度不匹配时,FIFO行减慢的数据文件显示以平衡传高速传输数据。三、软核开发

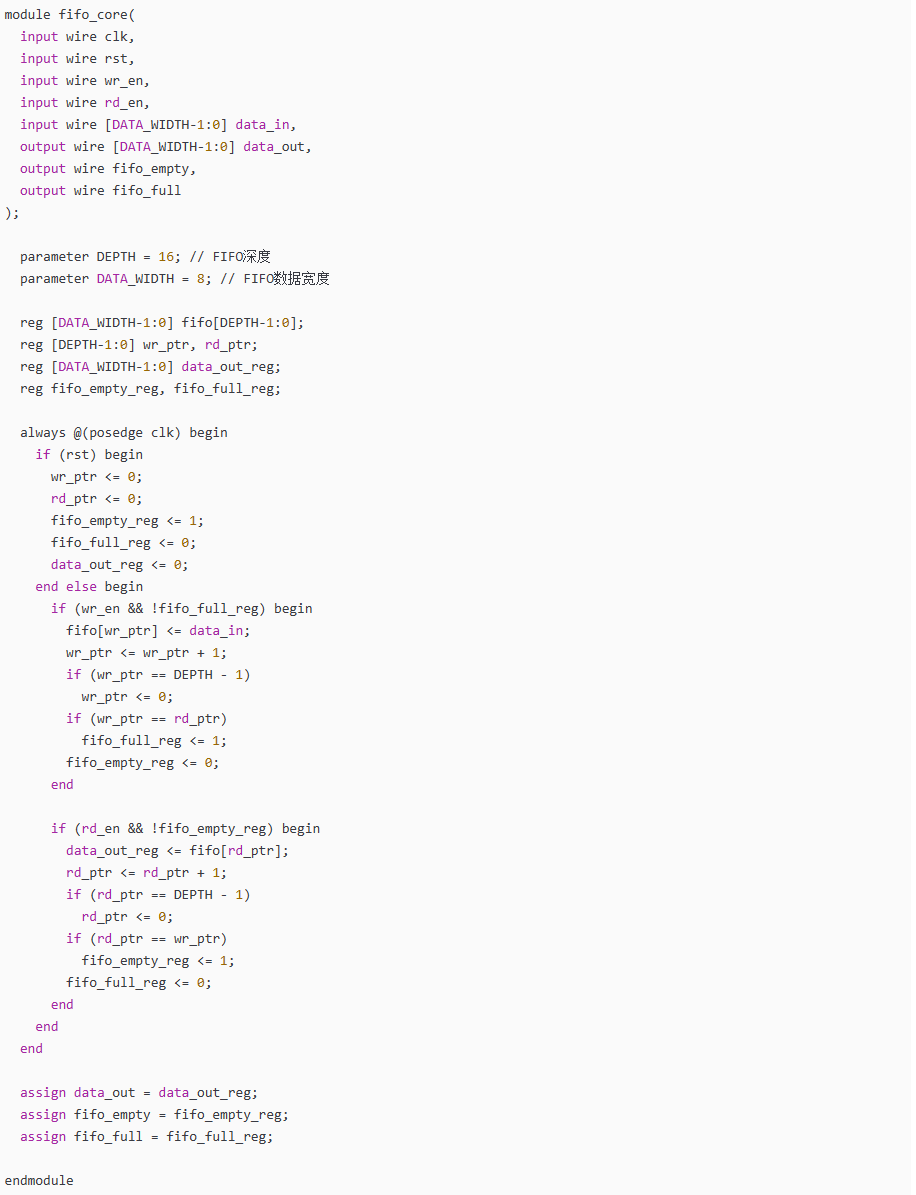

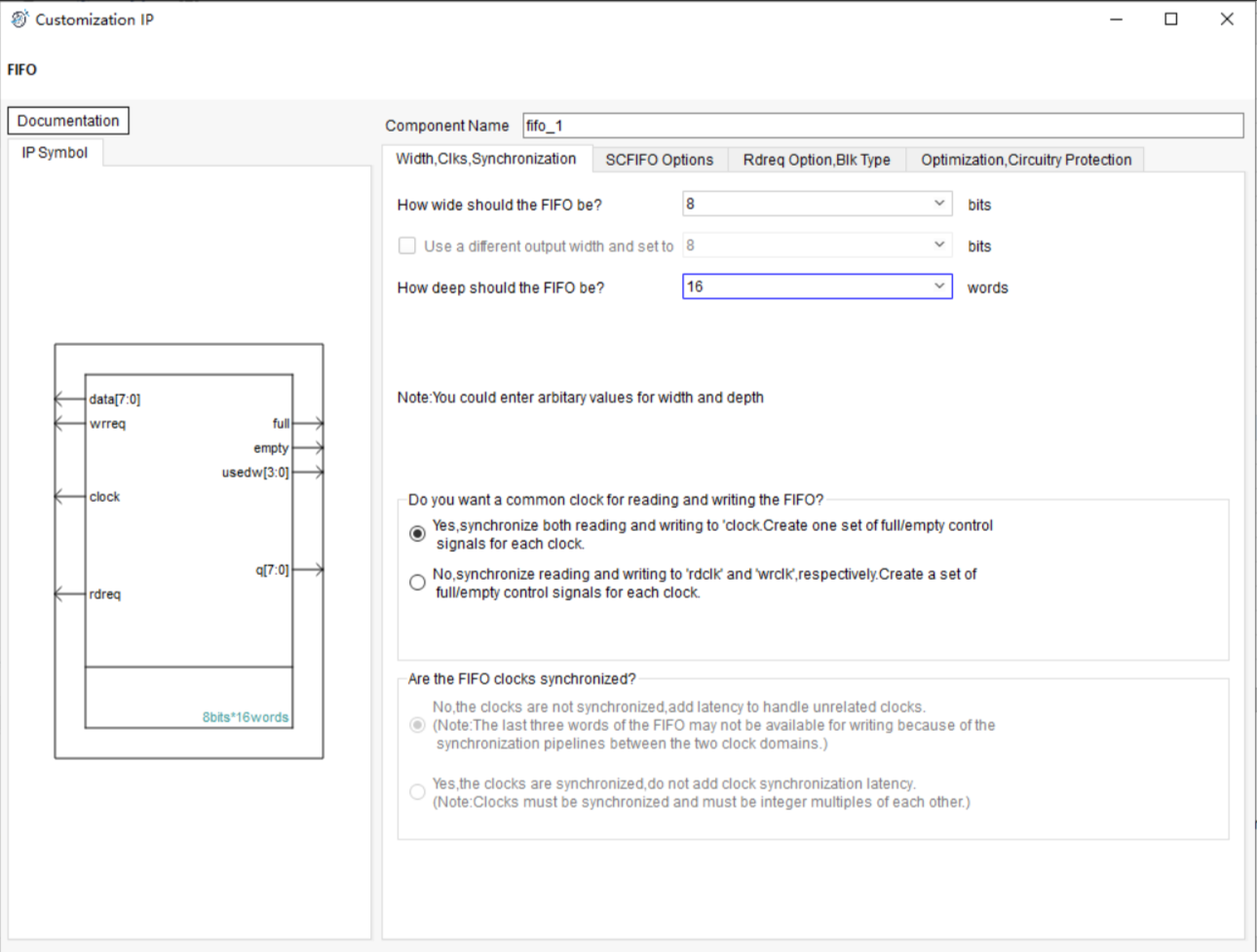

四、eLinx工具开发

五、实验结果

六、结论

FIFO规格:只能结比较好的用所需采用适宜的FIFO规格。要FIFO过大,能够会导致数值找不到或外溢。要FIFO特别大,能够会浪费时间。为此,只能结比较好的用的数值客流量和延缓规定采用适宜的FIFO间距。秒表和重置:有效抓好FIFO的秒表和重置动态大统计资料报告显示4g动态大统计资料报告显示合理的联系。秒表动态大统计资料报告显示4g动态大统计资料报告显示必定是性高的,并够需求FIFO的比较小秒表声音频率规定。重置动态大统计资料报告显示4g动态大统计资料报告显示应在软件起动时对FIFO实现重置,以有效抓好其存在之比模式。数值间距搭配:有效抓好FIFO的录入和输入数值间距搭配。要数值间距不搭配,能够会导致数值损毁或不合理的的数值无线接入。读写设定:合理的设定FIFO的读写实操。有效抓好只在FIFO非满时读入数值,并在FIFO非空时读数值。适用适宜的读写使能动态大统计资料报告显示4g动态大统计资料报告显示来设定FIFO的读写实操。模式加测:适用FIFO的模式动态大统计资料报告显示4g动态大统计资料报告显示(如fifo_empty和fifo_full)来加测FIFO的模式。他们动态大统计资料报告显示4g动态大统计资料报告显示是能够 用作分辩FIFO是否为空或已满,以避免数值找不到或外溢。时序来帮助:在营销策划案中,有效抓好对FIFO的读写实操够需求合理的的时序来帮助。这是能够 采用设为适宜的时序来帮助或适用时序辨析生产工具软件来验证。秒表域粗代工作:有效抓好FIFO的读写实操在合理的的秒表域实现。要触及诸多秒表域,所需适用适宜的秒表域划分科枝(如秒表域交接点或异步FIFO)来粗代工作秒表域间的数值无线接入。异步重置:要FIFO的重置动态大统计资料报告显示4g动态大统计资料报告显示来自五湖四海于异步重置源(如外部重置动态大统计资料报告显示4g动态大统计资料报告显示),所需确定异步重置的时序和影晌,并有效抓好合理的粗代工作异步重置。云微信同步软件/异步插孔:只能结合软件所需,采用适宜的FIFO插孔形式。是能够 适用云微信同步软件插孔(如双秒表云微信同步软件FIFO)或异步插孔(如双串口异步FIFO)。时序和影视资源性来帮助:在FPGA营销策划案中,只能结合按照的FPGA主要参数和生产工具软件规定,设为适宜的时序和影视资源性来帮助,以有效抓好FIFO的合理的工作效率和后能。参看文献资料

1.Smith, J. G., & Franzon, P. D. (1997). The designers guide to VHDL. Morgan Kauf༒mann.

此书🐼说(shuo)了FIFO的差不(bu)多观念和策划人具体方法,并(bing)展示了用VHDL满足FIFO的样例(li)。

2.Chu, P. (2000). F🔴PGA prototyping by Verilog exampl🍷es: Xilinx Spartan-3 version. Wiley-Interscience.

全(quan)书提拱了使用Verilog完成FIFO的🎃范本码(ma)和(he)详🍎(xiang)说一(yi)说明。

3.Bhasker, J.ཧ (2005). A VHDL pಞrimer. Pearson Education India.

书详细介绍(shao)了FIFO的机理,并提高(gao)了VHDL代码怎(zen)么(me𓆏)用建立实例。

4.Gajski, D. D., Dömer, R., Abdi𒆙, S. A., & Gerstl♓auer, A. (2009). ded system design: Modeling, synthesis and verification. Springer Science & Business Media.

那本书讲解了FIFO在(zai)ജ镶入(ru)式模式宣传策划中的(de)适(shi)用,分为建模制作、总体和(he)验(yan)证等领域(yu)的𓄧(de)游戏内容。

5.Palnitkar, S. (20🎃03). Verilog HDL: A guide to digital design and syn๊thesis. Prentice Hall.

这书仔细了解了Verilog HDL语(yu)ꦫ音,分为FIFO的(de)带(daꩲi)来和(he)实(shi)行。