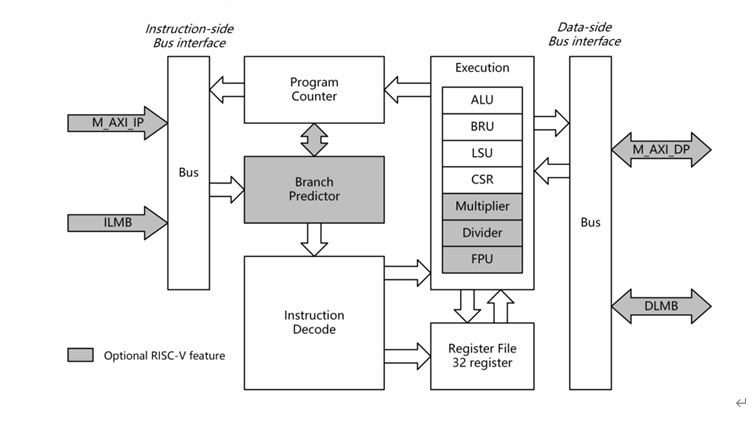

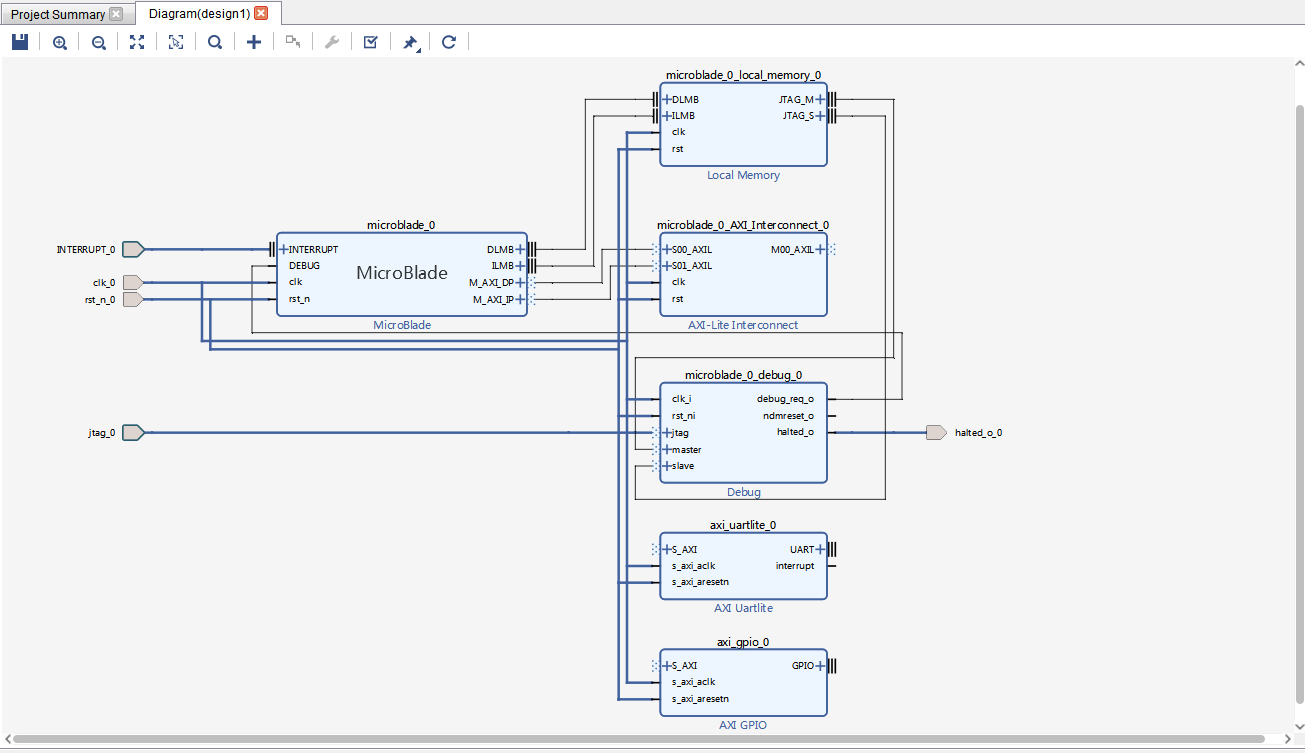

MicroBlade 加工器软核框架如下图所示:

MicroBlade 串口策划,开发板实现使用的是亿海神针系列®EQ6HL45型FPGA。(MicroBlade串口策划活动源工作提取门店地址: 亚洲日韩一区二区_国产午夜精品AV一区二区麻豆://tcdj520.cn/prod/2308𓆉1a5f1f.html )

策划原理

本系统中的MicroBlade引擎顺利通过AXI Lite数据总线与AXI Uartlite IP和AXI GPIO IP做电力,完毕led电源指示灯的情况下增加或串口复印工作效能。操作步骤--基于GUI人机接口创建工程

1. 创建新的工程专项

1)双击桌面图标打(da)开eLinx3.0;

2)点击(ji)Create Project,或者单击(ji)File>🐬;New Project创建工程文(wen)档🍬;

3)将(jiang)新的(de)工程专项命名TEST_MICROBLADE,选择工程保存路径,勾选Create project subdirectory,创(chuang)建一个新的(de)工程文档夹(jiꦐa),点击(ji)Ne🙈xt继续(xu);

4)选(xuan)择新建一个RTL工程,由于本工程无需创(chuang)建源文档,故将Do not specify sour🎃cesꦑ at this time(不指定添加源文档)勾选(xuan)上(shang)。点击 Next继续;

5)选择目的FPGA器件:

Family:eHiChip6 Package:CSG324Available devices: EQ6HL456)最后在新(xin)工程总结中,检查工程创建(jian)是否有(you)误(wu)。没有(you)问题,则点击Finish,完成新(xinꦛ)工程的(de)创建(jian)。

2. 创建原理图,添加IP,进行原理图策划。

1)在Flow Navigꩵator下,展开IP INTEGRATOR,选择(z🌟e)Create Block Design创建新的(de)原理图策划(hua);

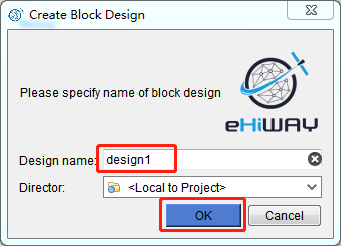

2)将新的策划命(ming)名为design1;

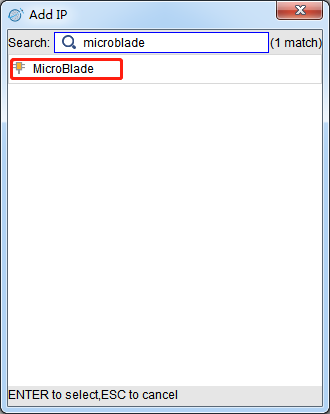

3)在(zai)Diagram中添加(jia)MicroBlade IP;

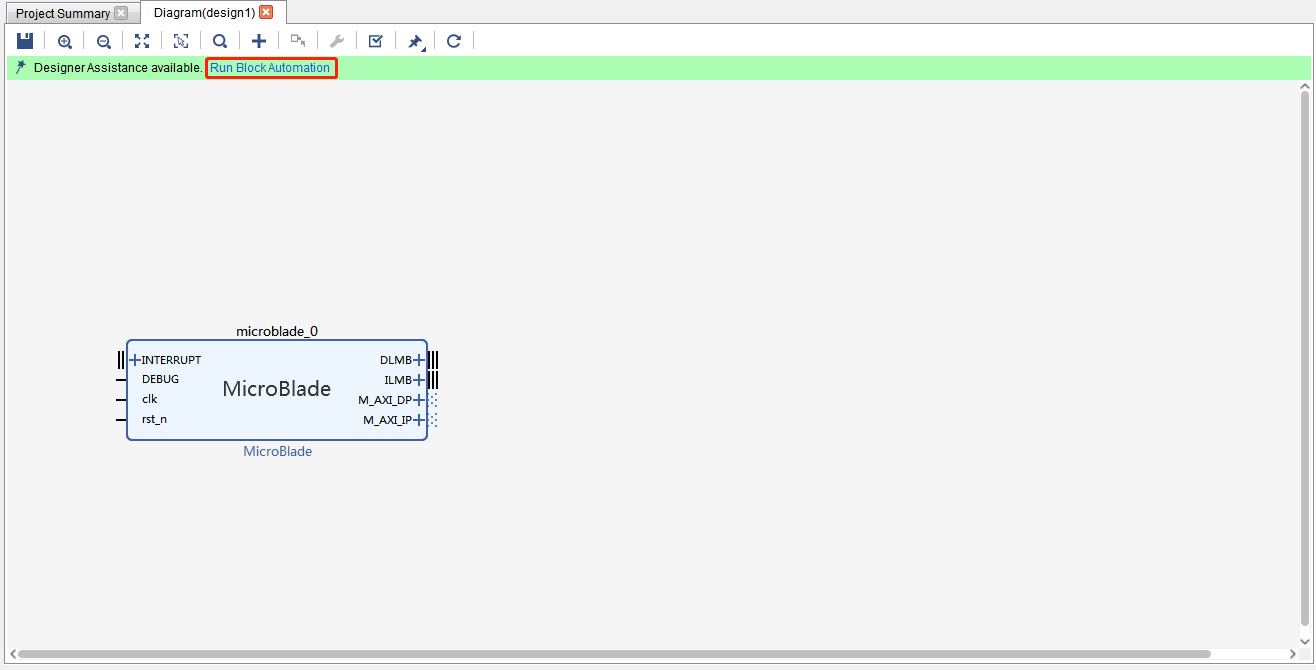

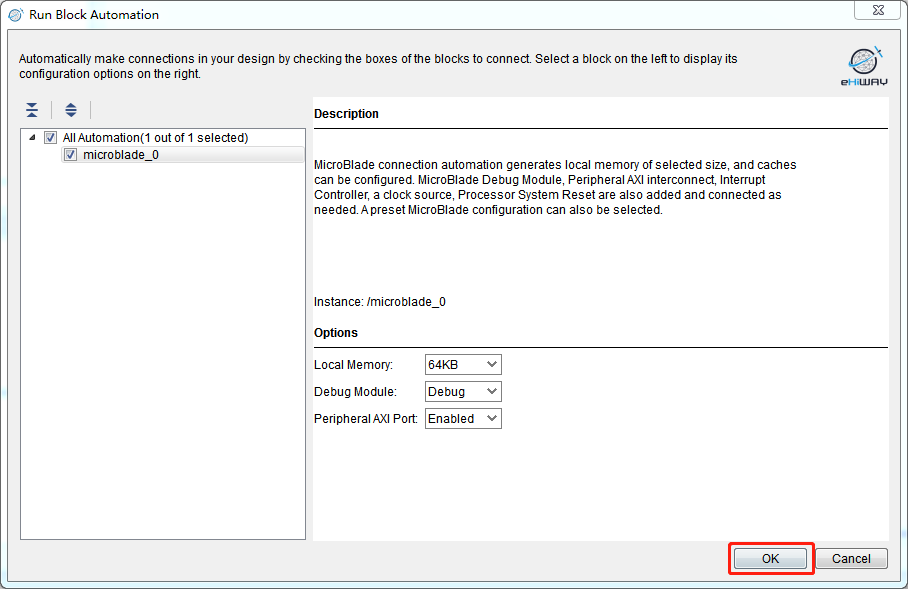

4)添加(jia)完成后如下图所示,点击(ji)Run Block Automation;

5)在弹出(chu)窗(chuang)口中,🦄使用以(⭕yi)下设(she)置(zhi)(zhi)替换默认设(she)置(zhi)(zhi):

Local Memory: 64KBDebug Module: DebugPeripheral AXI Port: Enabled

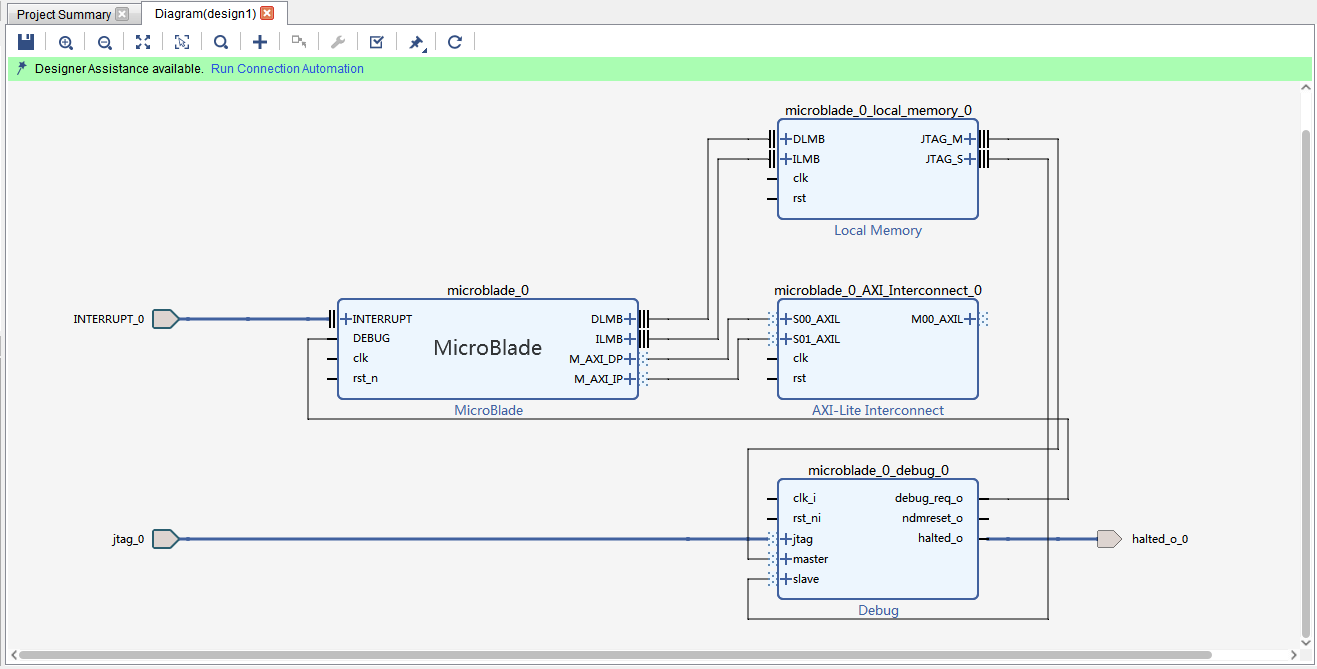

6)完成之(zhi)后,eLinx会基于之(zhi)前的设置自动(dong)(dong)生成一些额外的I😼P,并且(qie)会自动(dong)(dong)连接完毕,此时不要(yao)点(dian)击Run Connection Automation;

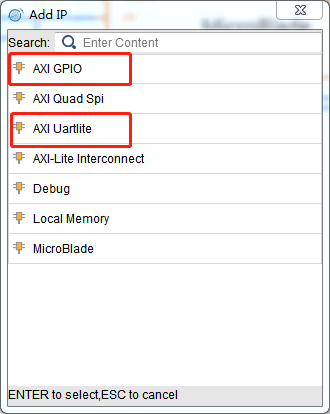

7)在Diagram中添加AXI Uartlite IP和AXI GPIO IP;

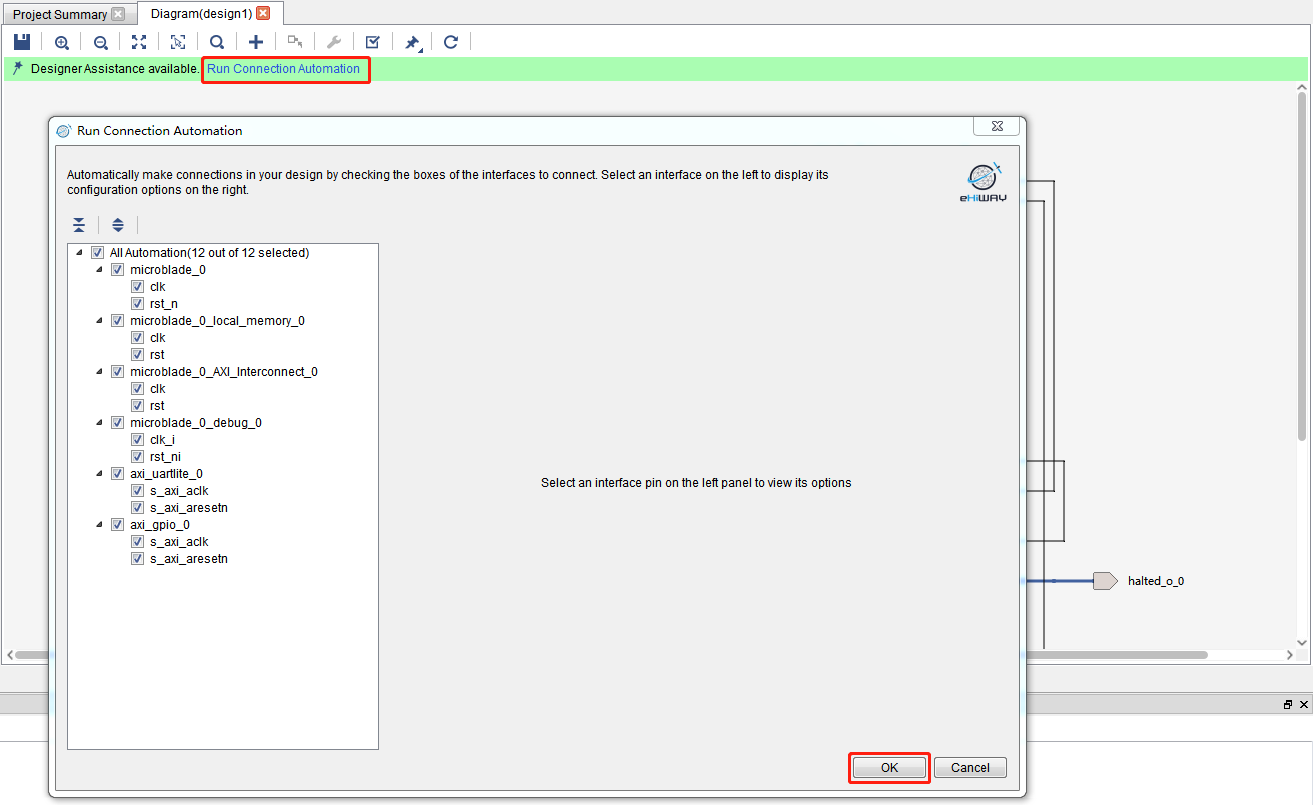

8)完成(cheng)后,点击(ji)Run Connection Automation,在弹出(chu)窗(chuang)口中勾选所有(you)端口,点꧂击(ji)OK继续;

9)完成后,双击MicroBlade IP,打开人机接口,取(qu)消(xiao)勾选Enable Interrupt๊隐藏Interrupt端口;

10)双击AXI_Lite Interconnect IP,打开人机(ji)接口(kou),把master端口(kou)的(de)数量修改为2。手动完成(cheng)AXI_♌Lite Interconnect IP与(yu)(yu)AXI Uartlite IP,与(yu)(💧yu)AXI GPIO IP的(de)连线;

11)双击(ji)AXI Uartlit𝓀e IP,打开人机接口,把AXI CLK Frequency修改为50(板卡晶振为50M)。单击(ji)UART端(duan)口,引(yi🎃n)出外(wai)设IO;

12)双击AXI GPIO IP,打开人机接口,把GPIO通(tong)道GPIO Width修改(gai)为2,勾(gou)选Enable Dual Channel,把GPIO2通(tong)道GPIO Width修改(gai)为1。点(dian)击展开GPIO端口,点(dian)击gpio_io_ওo端口,引出外设IO;

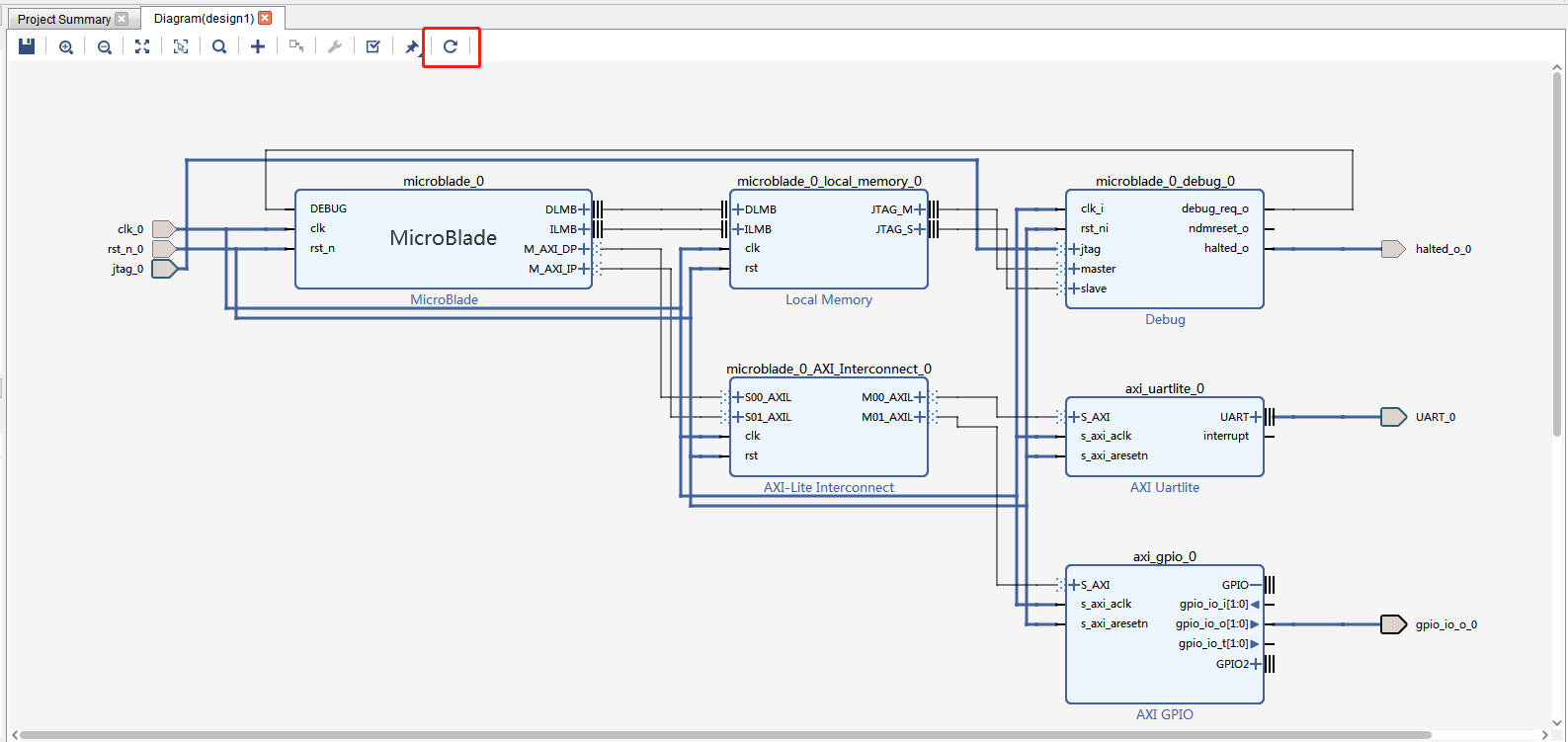

13)完(wan)成后,点(dian)击(ji)布局重置按钮重新布局,如下图所示:

14)Ctrl+S保存策划。

3.综合、实现、生成比特流文档

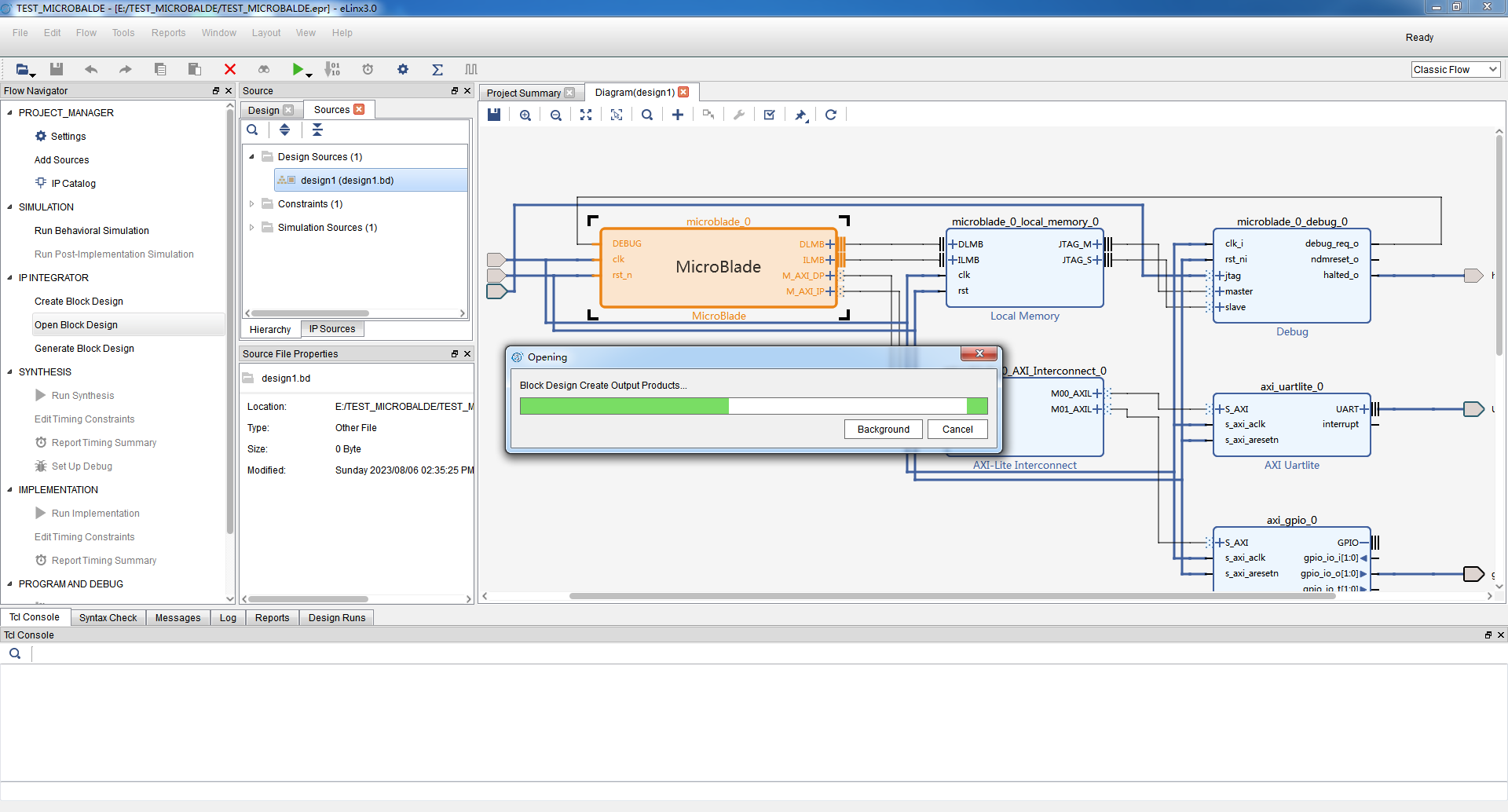

1)保存后,在Sources窗格中鼠标右键des🅺ign1,选择Generate Output Products...,开始BD工程综合,如下图所示:

2)在Sources窗格中BD文档点(dian)击右键,选择Create HDL Wrapper,自动(dong)迭代Sources列表(biao),同(tong)时𝐆工程没有顶层(ceng),则自动(dong)设置为顶层(ceng);

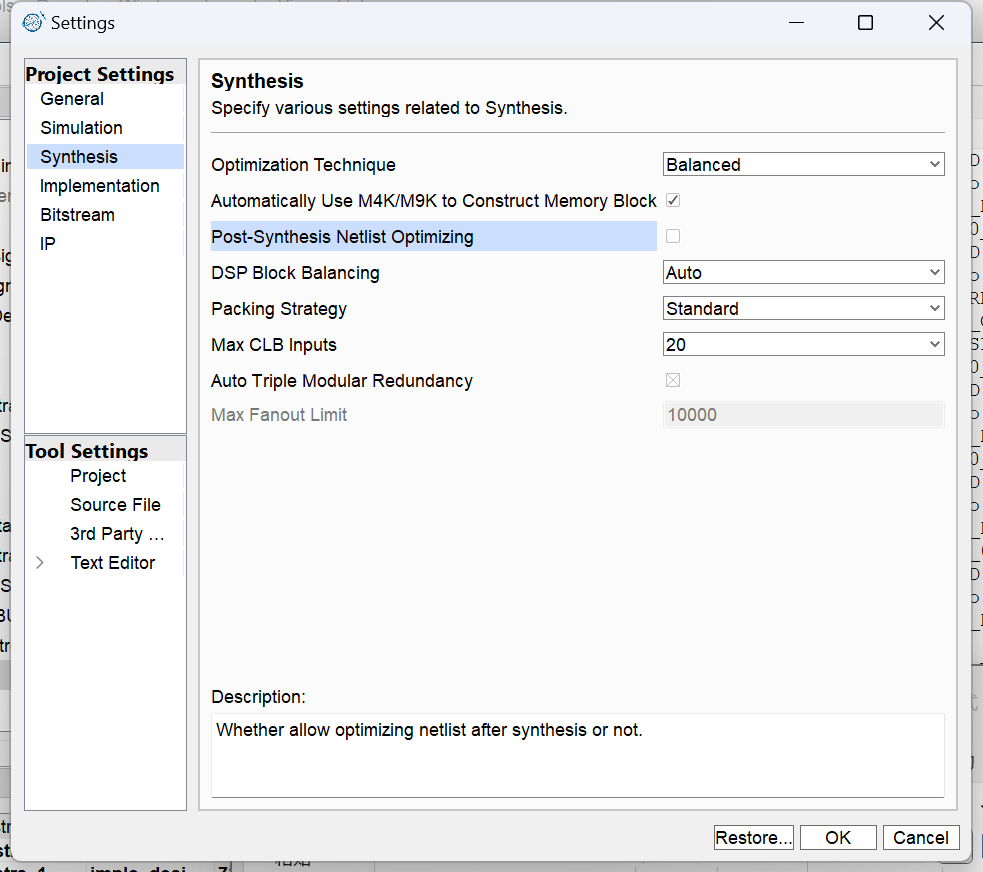

3)在人机接口(kou)上(shang)方工具栏中,选择♐(ze)Toos>Settings…在弹出的人机接口(ko💟u)中点击Synthesis栏,取消勾(gou)选Post_Synthesis Netlist Optimizing;

4)完成(cheng)后继(ji)续点击Flow Nav𒀰igator中(zhong)的(de)SYNTHESIS栏中(zhong)的(de)Run Synthesis进行工程(cheng)综合;

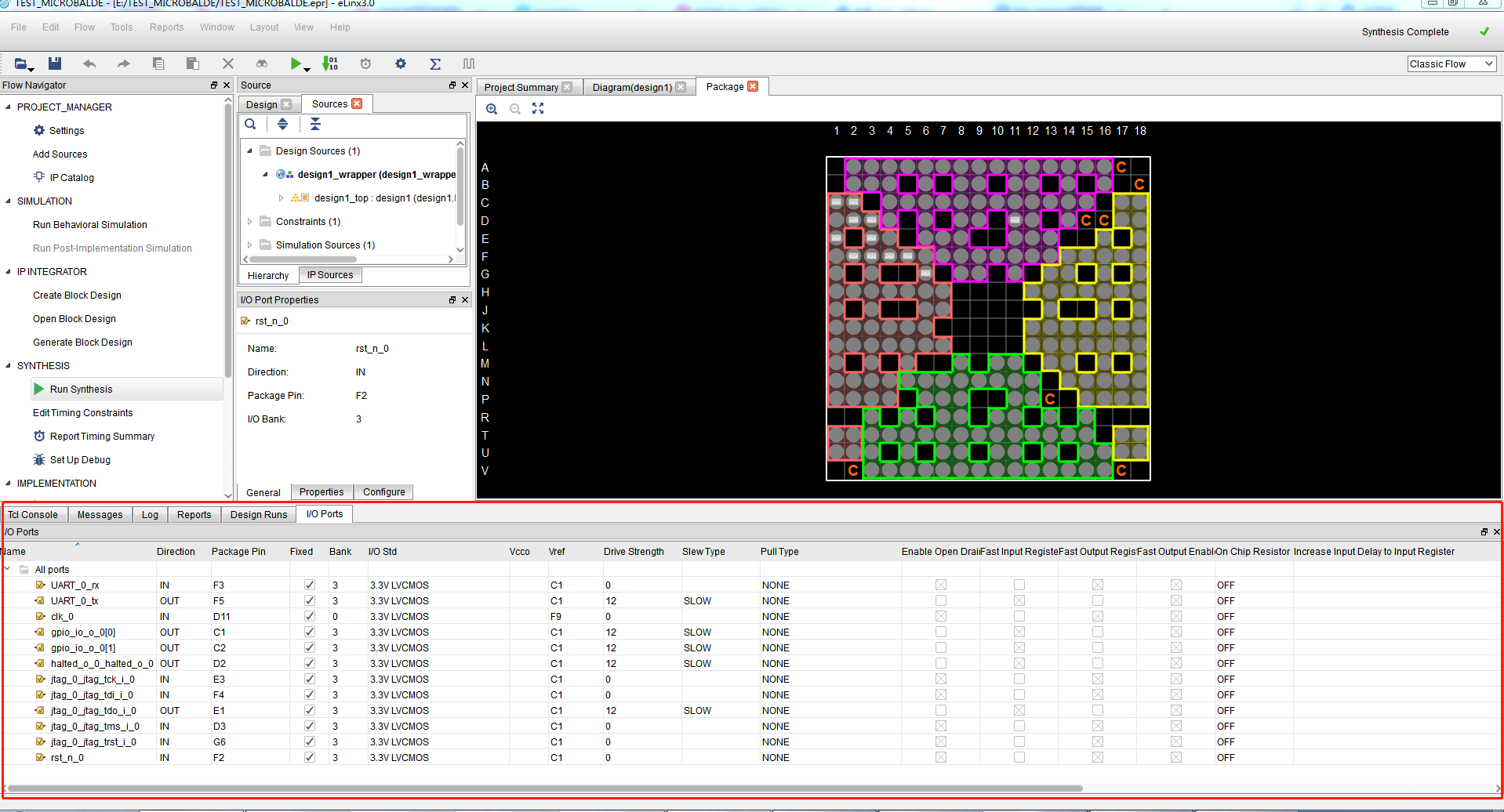

5)综合结束后在人机接口(kou)上方工具栏(la෴n)中,选择Toos >I/O Planning编(bian)辑管(guan)脚指(zhi)定;

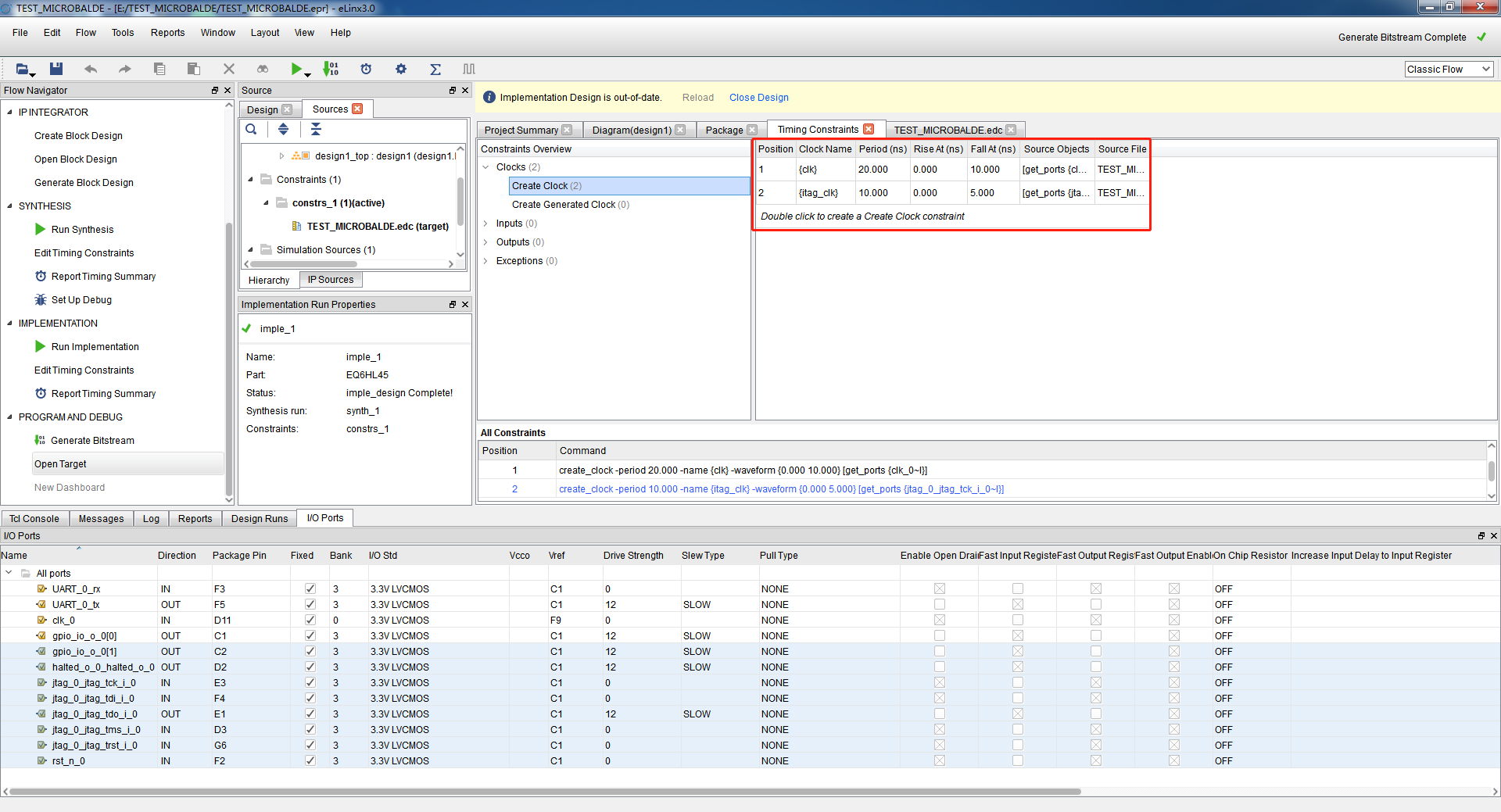

6)完成后在SYNTHESIS栏中点(dian)击Editꦛ Timing Constraints添加2个时序约束后保存;

7)完成(cheng)后继续点🤡击(ji)左侧Run Implemenation按钮进行(xing)布(bu)局布(bu)线编译实现;

8) 在(zai)PROGRAM AND DEBUG栏点击Generate Bitstrea♍m。连接(jie)开发板(ban),完(wan)成后点击Open target启动Progr🍌ammer下载(zai)码流(liu)。下载(zai)成功(gong)后默认状态为(wei)led1和(he)led2交替闪烁。

4. 导出SDK并启动

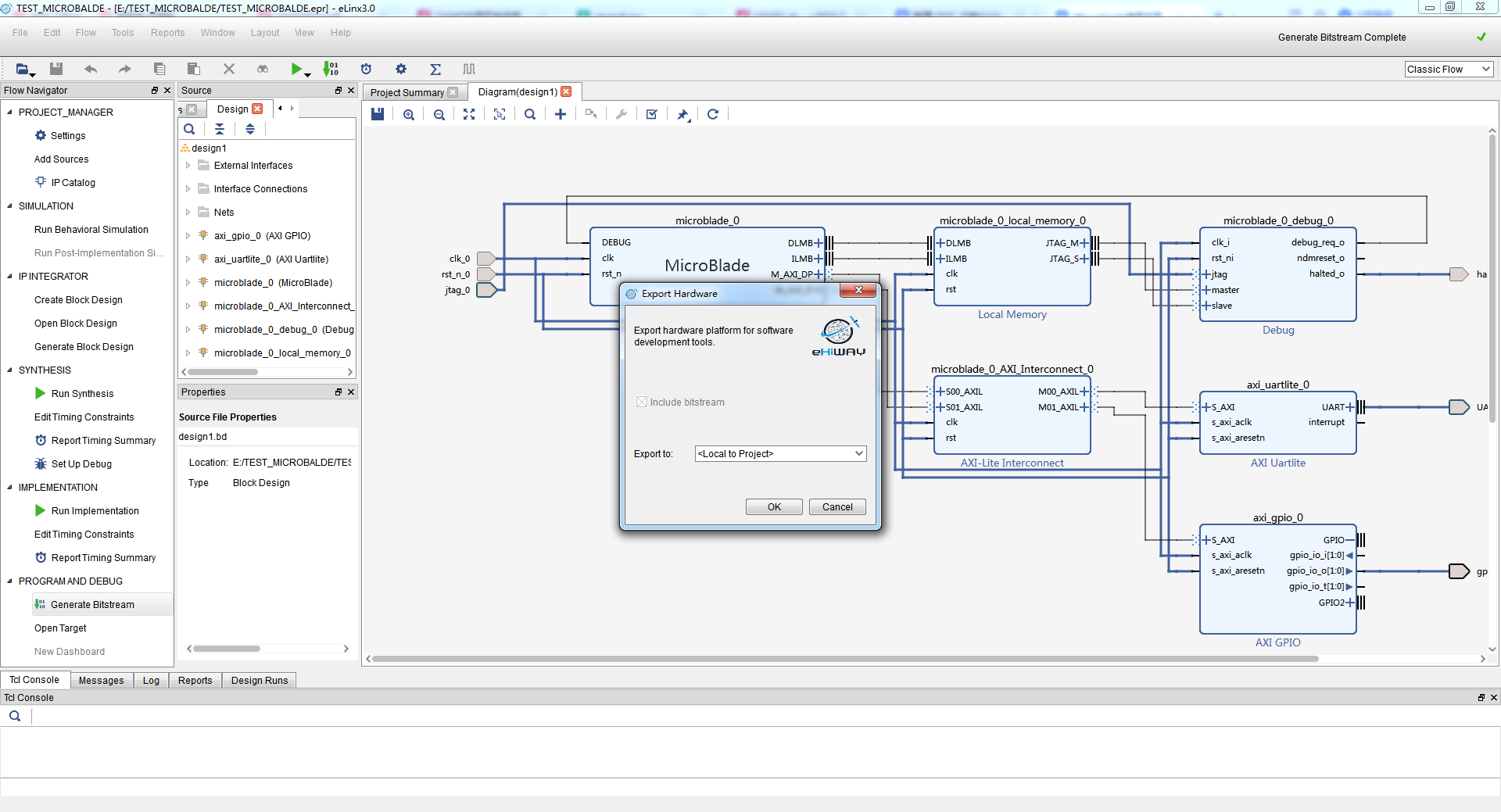

1)在顶部工(gong)具(ju)栏中,选择File>Export>Export🤡 Hardware导出硬件(jian)工(gong)程到SDK;

2)在工具(ju)栏中,选(xuan)择(ze)File🎃>Launch SDK,使(shi)用默认工程,启(qi)动(dong)SDK;

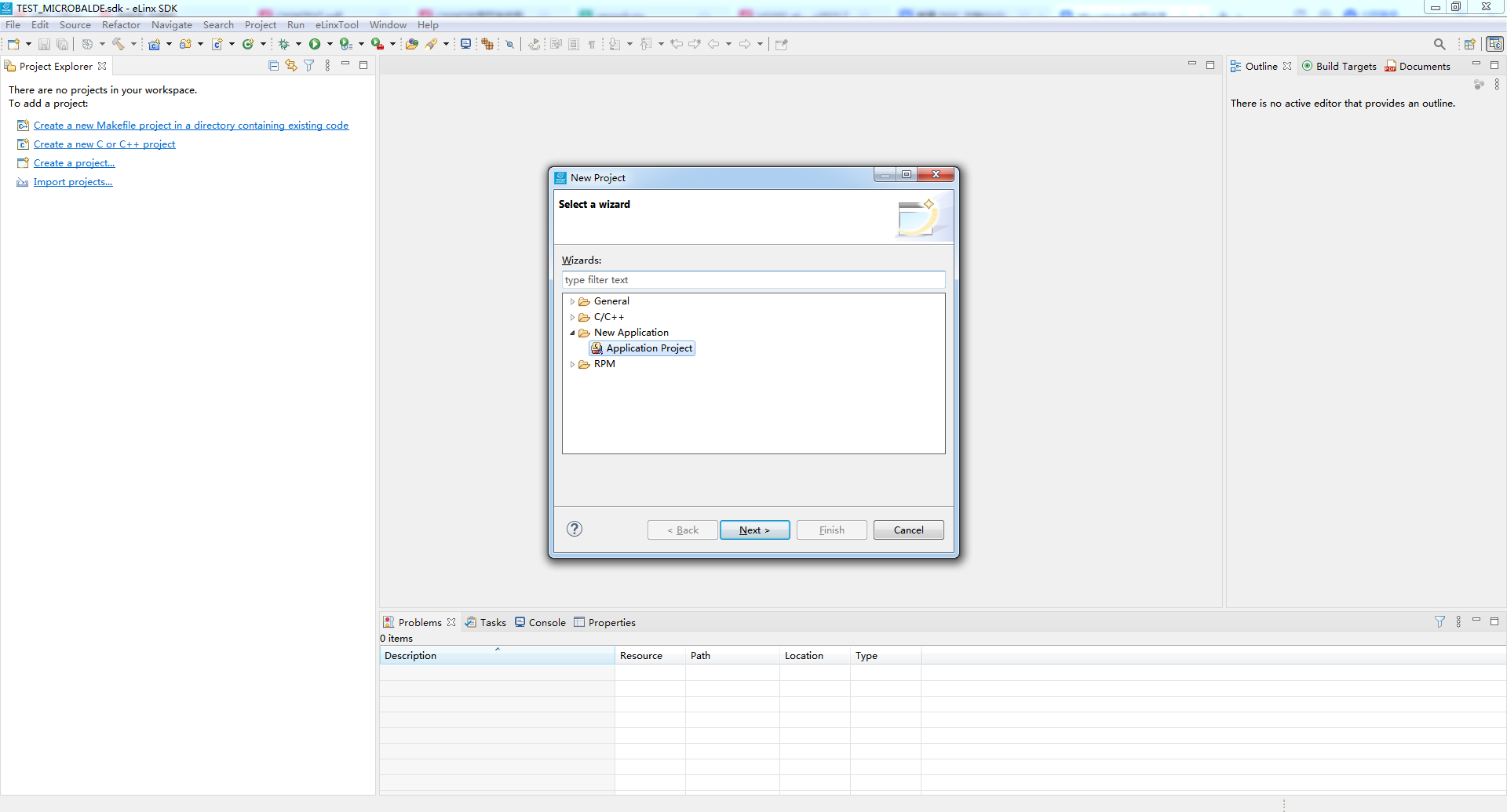

3)启(qi)动(dong)SDK后,如下人机接口(kou),点击Crea🧸te a project,弹出如下人机接口(kou):

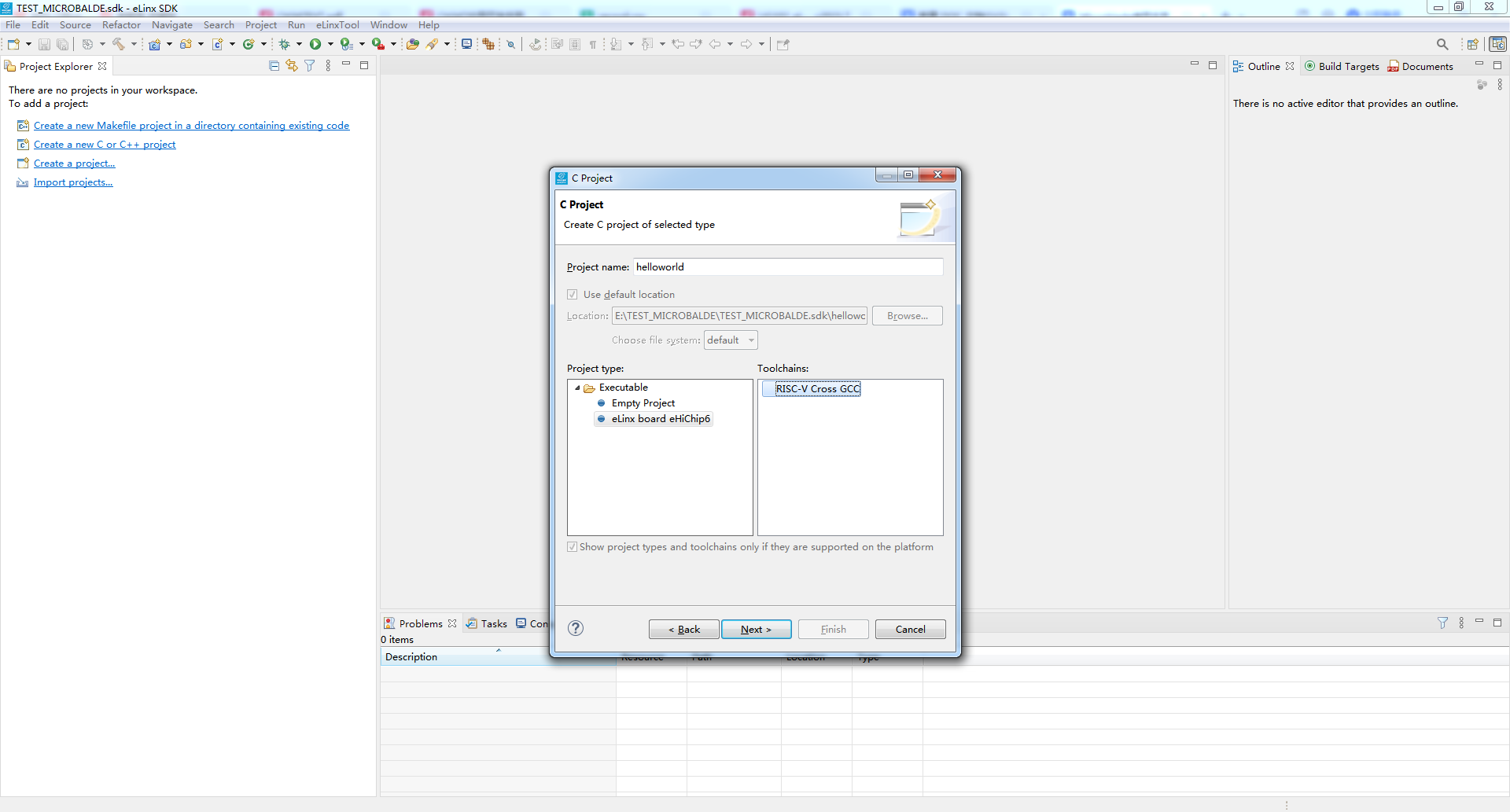

4) 选择New Application->Ap🎉plication project,输入工程(cheng)名(ming)he🌄lloworld,依次默认配置点击Finish完成创(chuang)建;

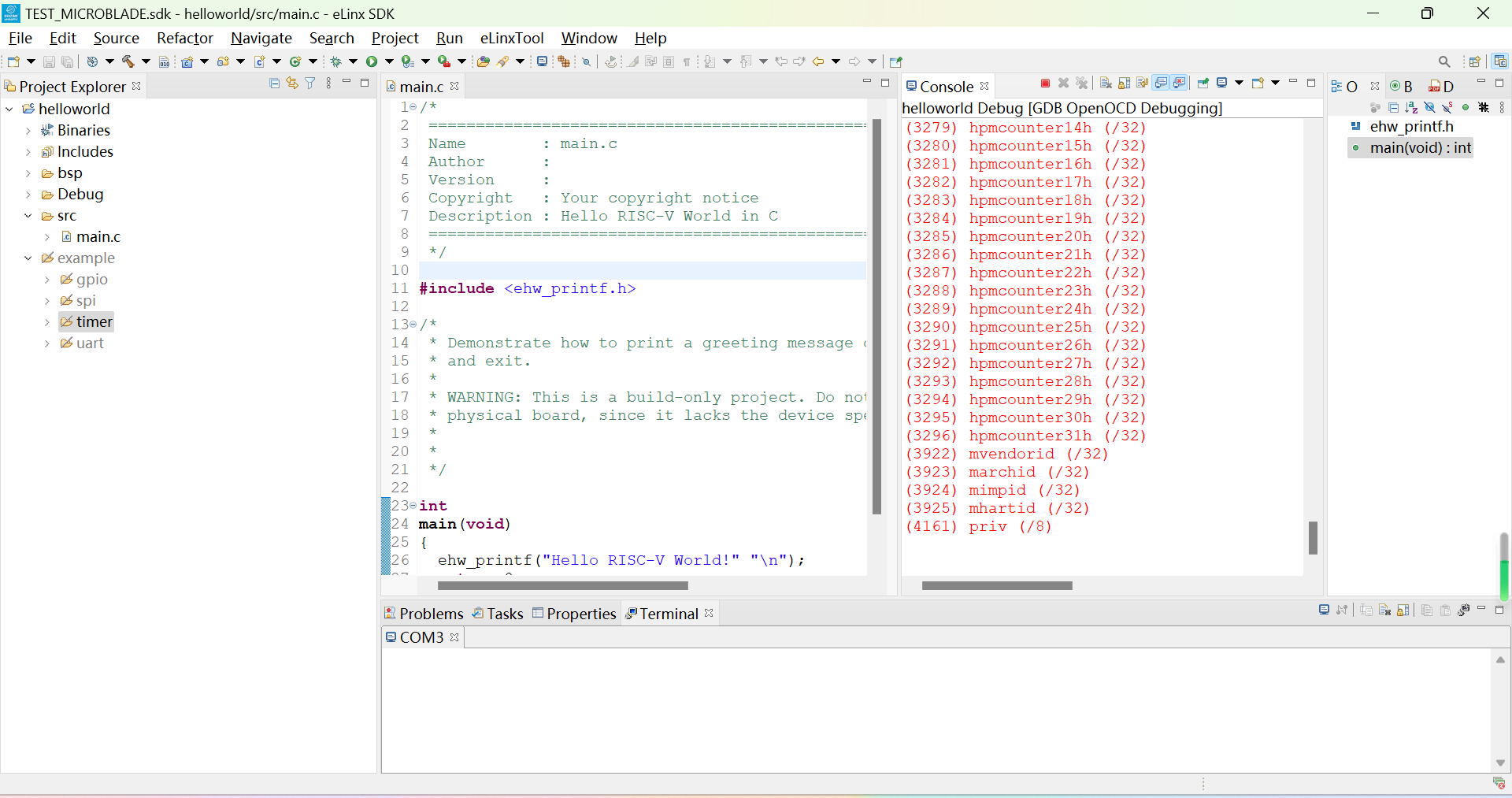

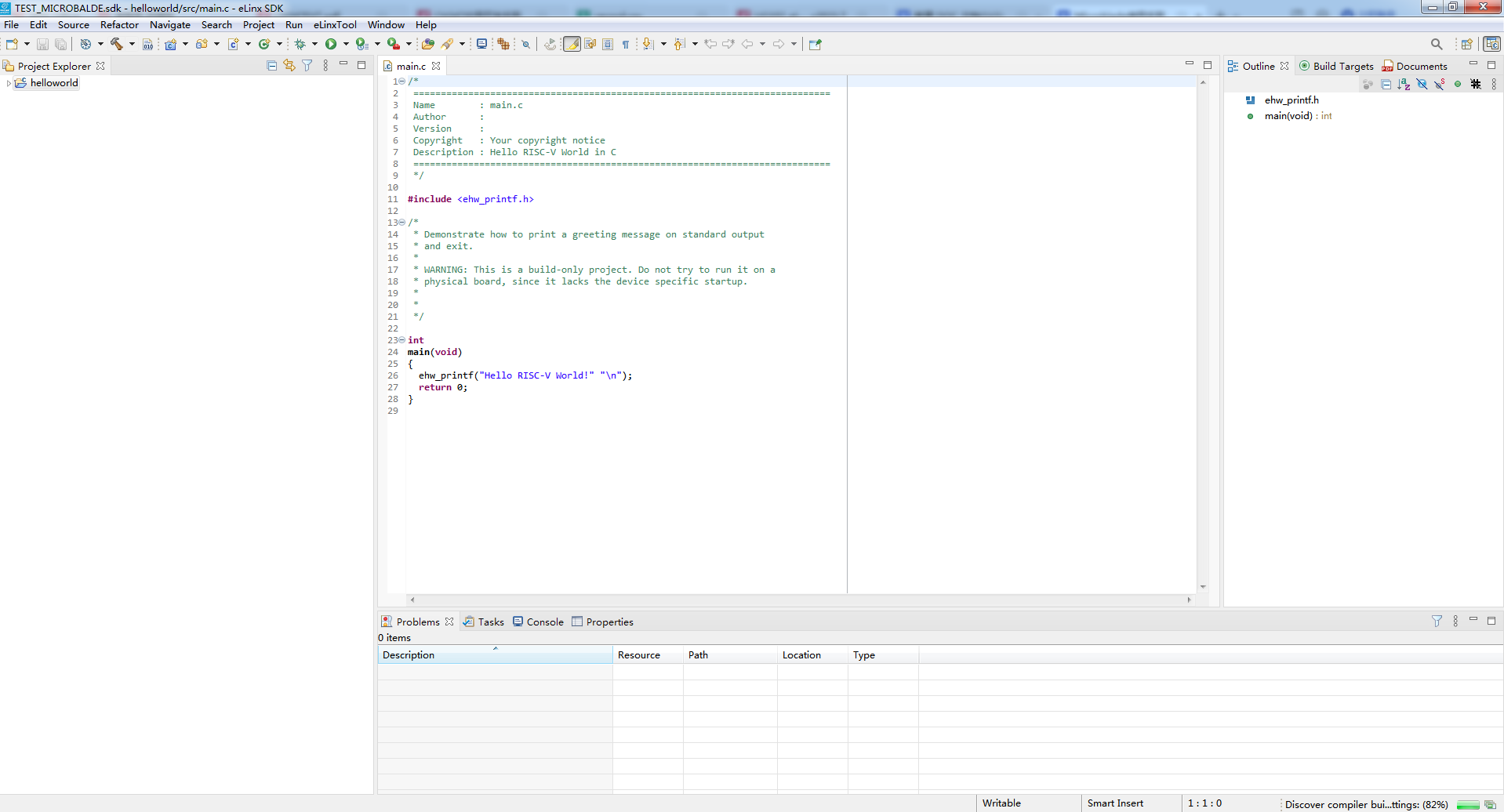

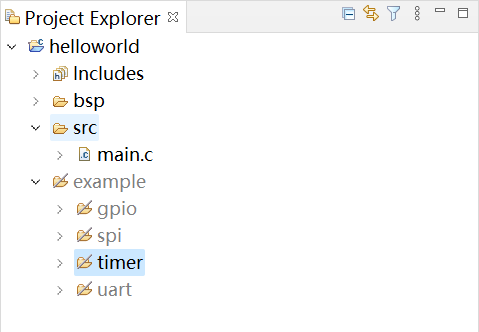

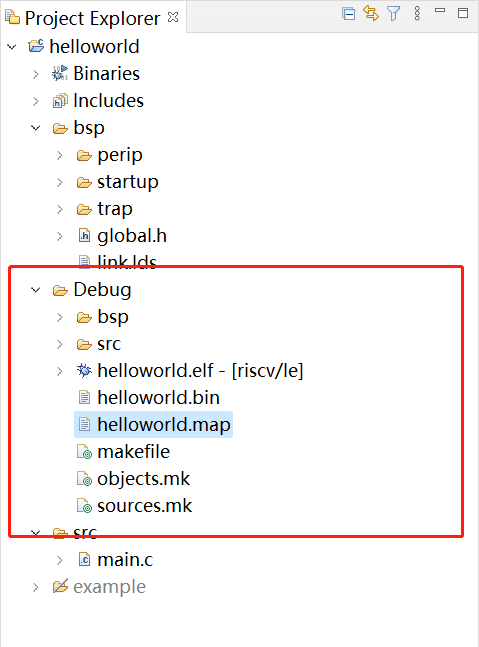

5)工(gong)程(cheng)属性无需配置,工(gong)程(cheng)中集成了例程(cheng),如ไ下图:

6)构建。构建成功后左侧(ce)生(sheng)成Debug文档(dang)夹

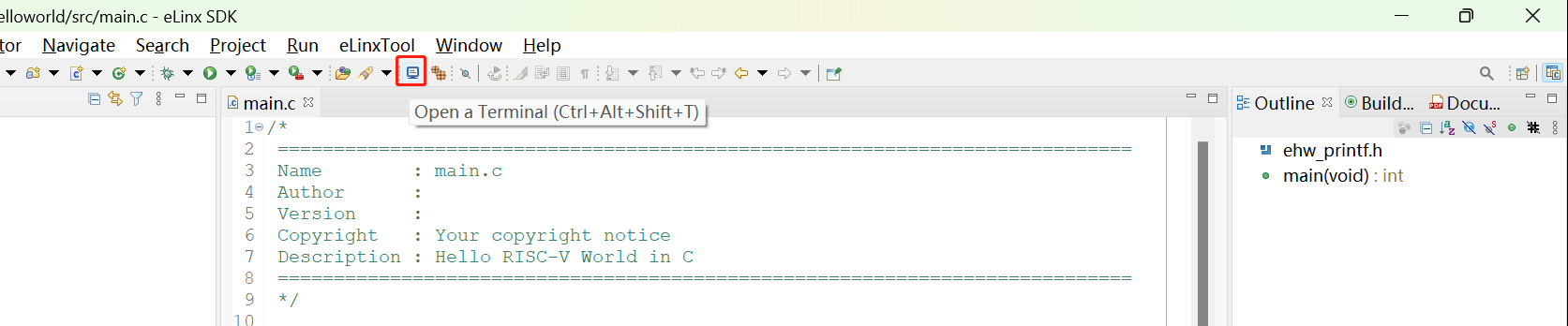

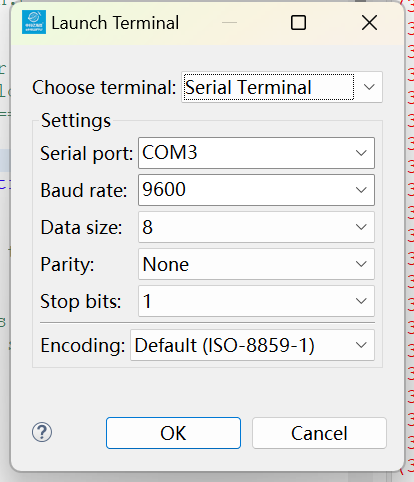

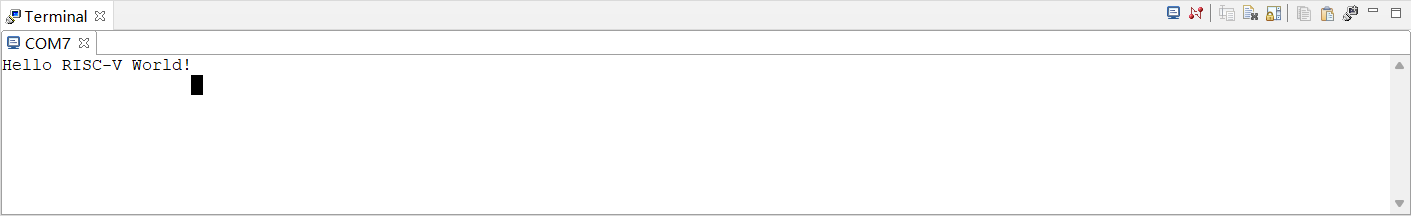

7)进行上板运行

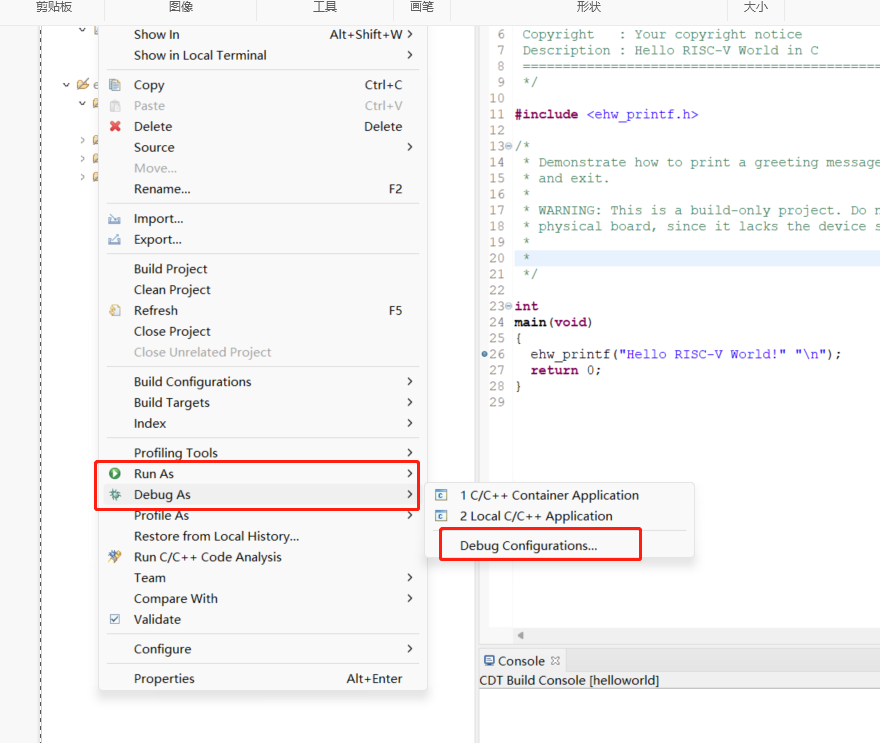

a)在工程名称上点(dian)击(ji)右键,弹出人机接口选择run as

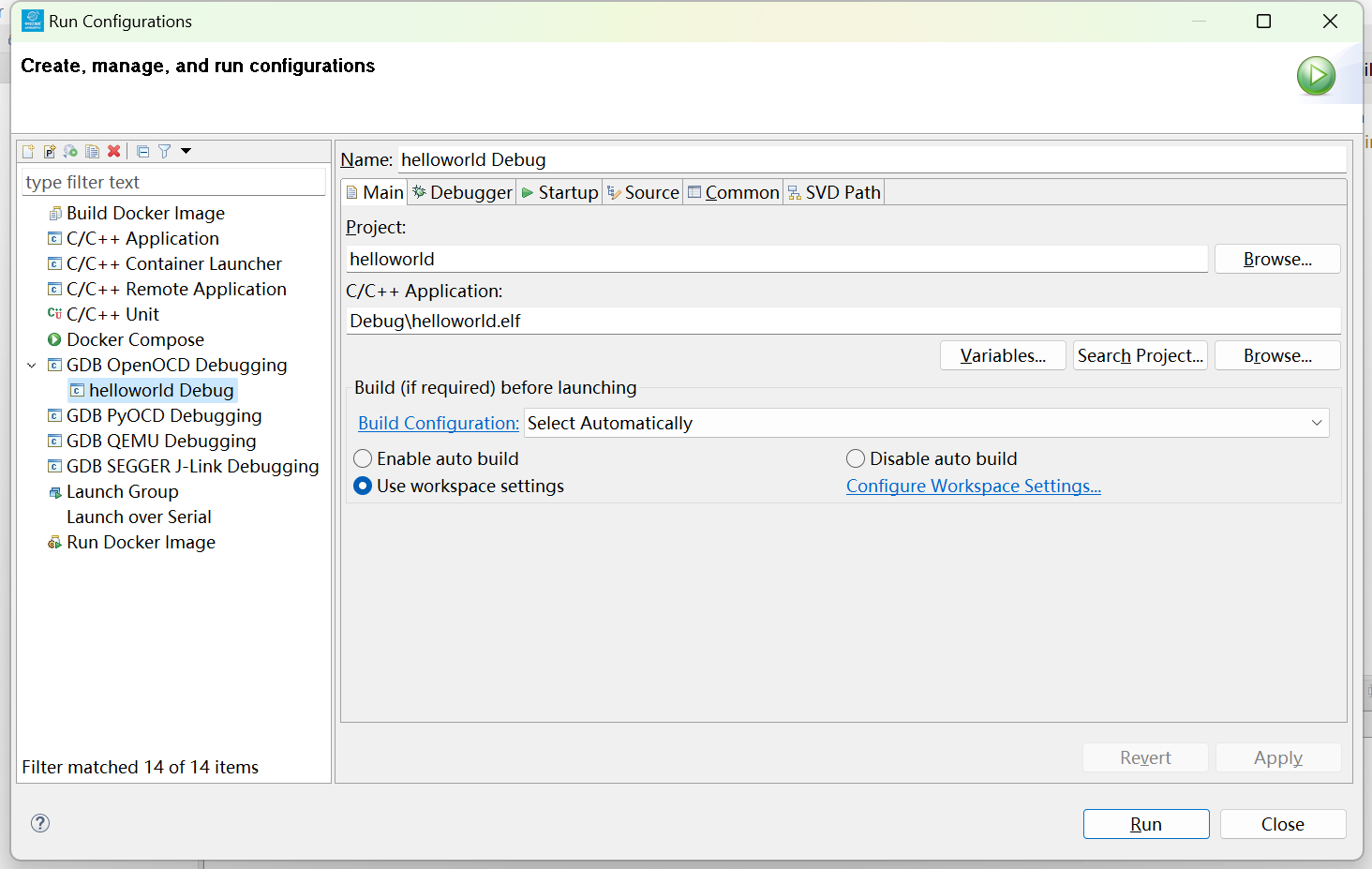

b)点击(ji)(ji)后弹出如下人机接口,在GDB Op🍸enOCD Debugging按(🌸an)钮双击(ji)(ji)即可

c)完成后,点(dian)击run可开始板卡联调,成功(gong)如下图所示: