发布(ꦛbu)日期:2022-10-12 作著:测封施工部 武浩(hao)然

1. 基本时序检查

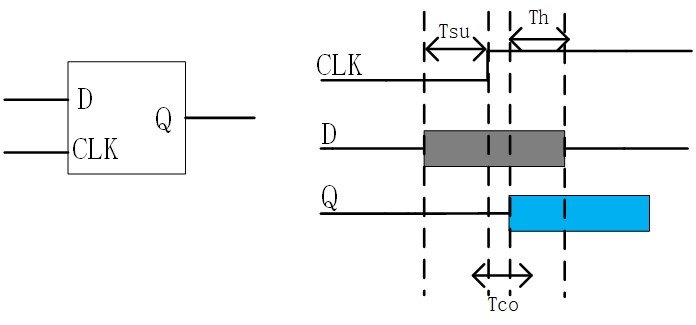

1) 运送沿:指运送数剧的源闹钟的活动边沿。2) 捕捉到边沿:指捕捉到数剧的目的秒表的活动边沿。3) 源秒表:指转发资料的秒表。4) 目的秒表:指抓取数据统计的秒表。5) 搭建要:选定义了最严格搭建定义的转发沿和阻止沿彼此的关联。6) 实现联系:指由时序解析工具验证的实现体检。7) 始终维持条件:特定义了最尖酸刻薄始终维持干涉的发送到沿和驯服沿相互之间的的关系。8) 保护的联系:指由时序解析工具验证的保护检修。2. 建立时间(Setup Time)

指的是在捕获器的闹钟电磁波飙升沿迎来半年前,的数据信息劳固改变的时段,即在CLK飙升沿来前一天,的数据信息须要提前就一名较小时段量首先需要做好准备好。3. 保持时间(Hold Time)

应是在开启器的闹钟无线信号提高的沿来临的时候,数据资料源稳定牢固未变的事件,即在CLK提高的沿来临后会,数据资料源须得恢复一款面积最小事件量可以转变。4. D触发器介绍

5. 时序解析原理

相对 一些FPGA策划案,在获得了了相应对的的繁多用时指标、用时延迟,就可便于用相应对的的冗余时序解答道具来对其现在进行时序解答工作中。今天以“如何通出众脑来展开序解析” 装修案例来展开详详说明。

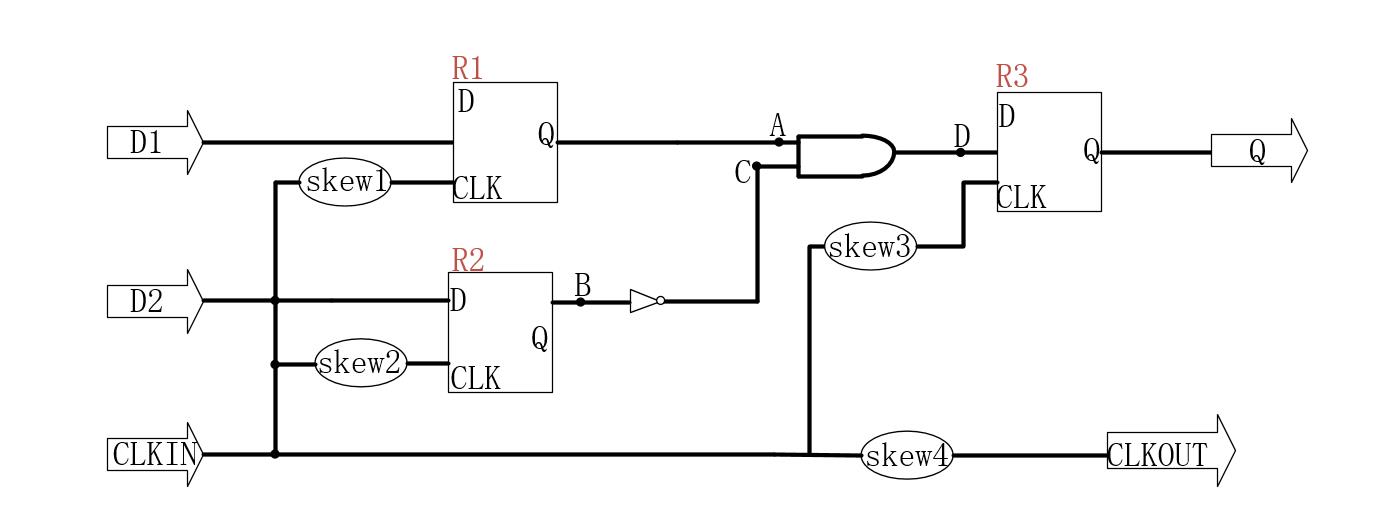

6.解析电路

以上FPGA控制线路系统能不能健康人的做工作上但关键在于于3个标准:一号,入乎部的每一个寄存器能不能健康人的做工作上;其三,Q与CLKOUT的关系的能不能满意后级控制线路系统的规范。如再相关性,FPGA电子器件能不能健康人的做工作上但关键在于于六个标准:一号,能不能科学合理地信息采集间接数剧;其三,FPGA内部管理能不能科学合理地加工处理数剧;其三,FPGA的打印输出是否满意后级控制线路系统的规范。针对于3个要求的细分措施,要求一和要求三虽然数剧流方向有差异,但其共性是跟自身沟通,所以说可融合叫做FPGA的标准接口要求。相应对的,要求二可叫做内层闹钟要求。一方面,为正个FPGA策化特定考生0经常,并令0经常时,CIKIN处正好来临另一个闹钟的上升沿。由于(yu)本(ben)例(li)电(dian)路中(zhong)的(de)寄(ji)存器(qi)(qi)在每个(ge)时钟(zhong)有效边沿时刻(ke)所面临的(de)工(gong)作状态(tai)都(dou)是(shi)(shi)一(yi)样的(de),因(yin)此,在每同(tong)一(yi)个(ge)寄(ji)存器(qi)(qi)还有后级电(dian)路系统(tong),只必(bi)须(xu) 详细分(fen)析6个(ge)边沿情況即可(kꦐe)。那么,以(yi)0经常的(de)闹(nao)钟(zhong)升沿为参考价值(zhi),在寄(ji)存器(qi)(qi)R1来说,有用(yong)闹(nao)钟(zhong)升沿传递到其闹(nao)钟(zhong)网(wang)(wang)络网(wang)(wang)络网(wang)(wang)口(kou)的(de)时間0ns+skew1=4ns,无可(ke)厚非(fei),一(yi)切正(zheng)常工(gong)作时,它是(shi)(shi)会精准(zhun)采样系统(tong)到D1网(wang)(wang)络网(wang)(wang)络网(wang)(wang)口(kou)从-10ns确保(🔴bao)到10ns的(de)大数据(ju)(ju)分(fen)析标(biao)符。鉴于(yu)2ns线延迟的(de)影晌,导至R1的(de)D网(wang)(wang)络网(wang)(wang)络网(wang)(wang)口(kou)上(shang)分(fen)别的(de)大数据(ju)(ju)分(fen)析固牢差值(zhi)会是(shi)(shi)-8ns~12ns。据(ju)(ju)图可(ke)为之出寄(ji)存器(qi)(qi)R1的(de)确立期限和(he)确保(bao)期限方式:

Tsu = 4 - (-8) = 12nsTh = 12 -4 = 8ns因Tsu >= 2ns、Th >= 1ns,故R1就能够常规办公。7. 时序约束语句

对待所有的时序途径,我们也要明晰其起步和终端,这4类时序途径的起步和终端各自如下表下图。| 时序路径 | 应用约束 |

| (1)输入端口到FPGA内部第一级触发器的路径 | set_input_delay |

| (2)FPGA内部触发器之间的路径 | create_clock |

| (3)FPGA内部末级触发器到输出端口的路径 | set_output_delay |

| (4)FPGA输入端口到输出端口的路径 | set_max_delay |

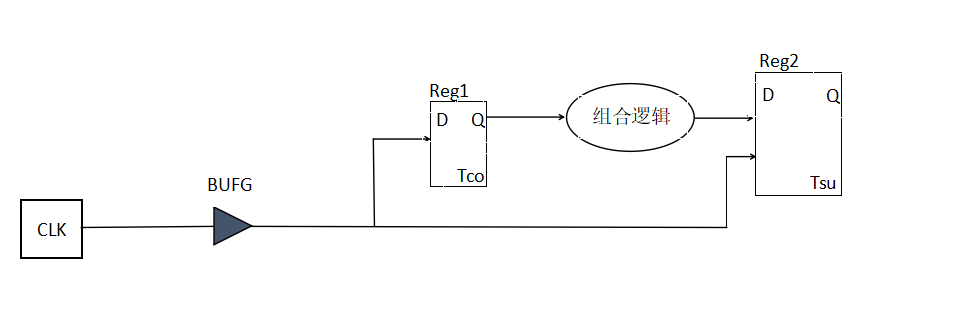

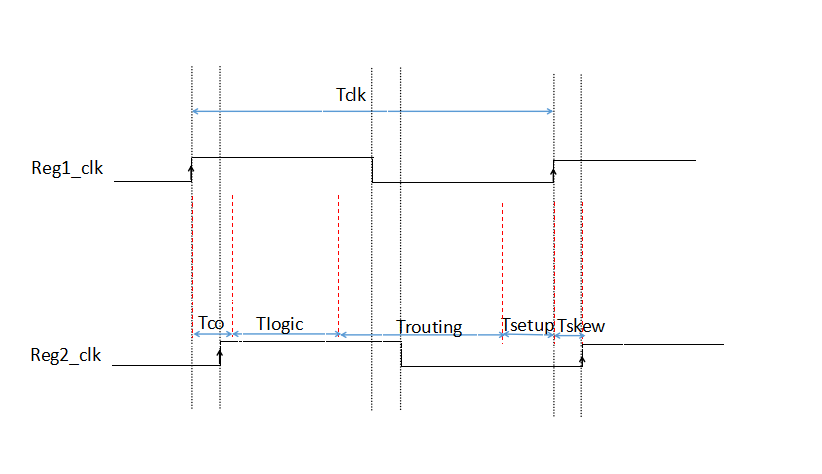

8. 时序模型

明显的时序实体建模 如下面的图如下图所示。同一个完正的时序绝对路劲分析包含源秒表绝对路劲分析、数剧绝对路劲分析和目的秒表绝对路劲分析,也可以表示为驱散器+组成逻辑关系+驱散器的实体建模 。

9.时序约束

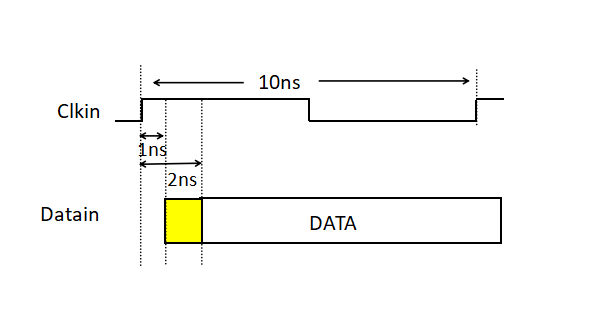

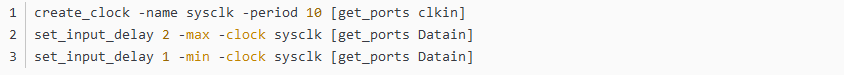

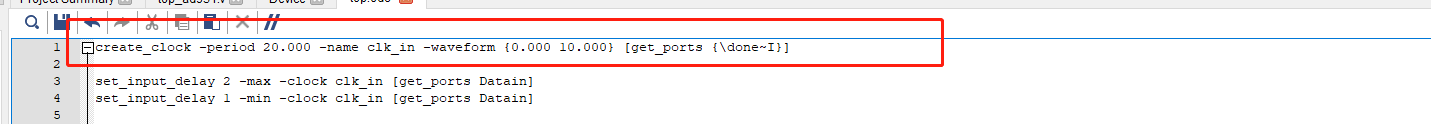

延迟约束:延(yan)迟约束(shu)用的是(shi)(shi)set_input_delay和set_output_delay,分别用于input端和output端,其♌时钟源可以是(shi)(shi)时钟输(shu)入管脚,也可以是(shi)(shi)虚拟(ni)时钟。但需要注(zhu)意(yi)的是(shi)(shi),这两个(ge)约束(shu)并不是(shi)(shi)起延(yan)迟作用,具(ju)体(ti)原因解析如(ru)下(xia)。

inputDelay(max) = Tco(max) + TD(max)inputDelay(min) = Tco(min) + TD(min)

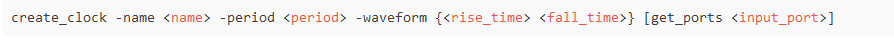

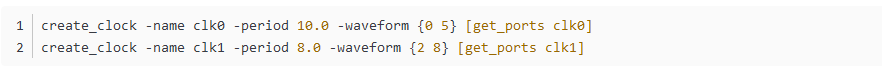

| 参数 | 含义 |

| -name | 时钟名称 |

| -period | 时钟周期,单位为ns |

| -waveform | 波形参数,第一个参数为时钟的第一个上升沿时刻,第二个参数为时钟的第一个下降沿时刻 |

| -add | 在同一时刻源上定义多个时钟时使用 |

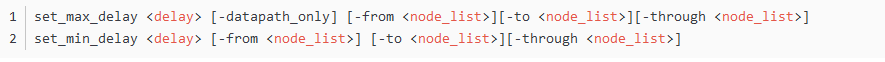

最大/最小延迟约束: 顾名思义(yi),就是设置路径的max/min delay,主要应用🍸场(chang)景有(you)两个(ge),①输(shu)入管(guan)脚的信号经过组合逻(luo)辑后(hou)直接输(shu)出到(dao)管(guan)脚;②异(yi)步(bu)电路之间的最(zui)大最(z🥃ui)小(xiao)延迟。

| 参数 | 含义 |

| -from | 可以有效的始点子域包含了:石英钟、input(input)服务器端口或时序单元测试(寄存器,RAM)的石英钟引脚。 |

| -to | 有效的终止节点包含:时钟、output(inout)端口或时序单元的数据端口。 |

| -through | 有效的节点包含:引脚、端口、线网。 |

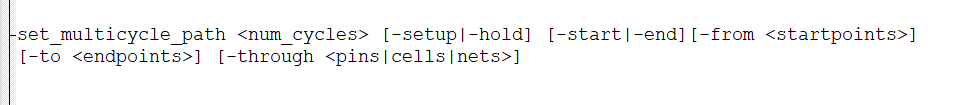

多周期路径约束:在(zai)频(pin)次性管(guan)(guan)束(shu)(shu)(shu)的(de)(de)(de)(de)(de)的(de)(de)(de)(de)(de)功(gong)效下(xia)(xia),时(shi)序解释工(gong)具(ju)会认同该挂(gua)(gua)钟(zhong)域内寄(ji)存器的(de)(de)(de)(de)(de)打出在(zai)所(suo)有(you)挂(gua)(gua)钟(zhong)案件的(de)(de)(de)(de)(de)降临(lin)都会变(bian)化,所(suo)以,良(liang)好具(ju)体情(qing)况下(xia)(xia)所(suo)有(you)寄(ji)存器的(de)(de)(de)(de)(de)始(shi)终保持的(de)(de)(de)(de)(de)时(shi)间均为个(ge)挂(gua)(gua)钟(zhong)频(pin)次。但是(shi)有(you)时(shi)刻,FPGA营销策(ce)划(hua)的(de)(de)(de)(de)(de)工(gong)作效能的(de)(de)(de)(de)(de)特点绝对(dui)(dui)前级寄(ji)存器必须经过(guo)(guo)(guo)多(duo)挂(gua)(gua)钟(zhong)频(pin)次后才会变(bian)化,这(zhei)样首先,假若实际(ji)上对(dui)(dui)该挂(gua)(gua)💛钟(zhong)域获取频(pin)次管(guan)(guan)束(shu)(shu)(shu),虽然对(dui)(dui)这(zhei)篇(pian)(pian)(pian)分(fen)电路(lu)(lu)(lu)系统(tong)板(ban)(ban)设(she)(she)计是(shi)过(guo)(guo)(guo)管(guan)(guan)束(shu)(shu)(shu)了。假若这(zhei)篇(pian)(pian)(pian)分(fen)电路(lu)(lu)(lu)系统(tong)板(ban)(ban)设(she)(she)计的(de)(de)(de)(de)(de)语(yu)言(yan)(yan)表(biao)达(da)(da)比较容易,过(guo)(guo)(guo)管(guan)(guan)束(shu)(shu)(shu)并(bing)并(bing)不会带去甚么大毛病,但假若这(zhei)篇(pian)(pian)(pian)分(fen)电路(lu)(lu)(lu)系统(tong)板(ban)(ban)设(she)(she)计的(de)(de)(de)(de)(de)语(yu)言(yan)(yan)表(biao)达(da)(da)较为复(fu)杂,过(guo)(guo)(g🦋uo)管(guan)(guan)束(shu)(shu)(shu)很或(huo)许会导致(zhi)时(shi)序解释的(de)(de)(de)(de)(de)时(shi)刻不互通过(guo)(guo)(guo)。所(suo)以,方便是(shi)可以科学合理(li)地对(dui)(dui)这(zhei)篇(pian)(pian)(pian)分(fen)语(yu)言(yan)(yan)表(biao)达(da)(da)获取时(shi)序管(guan)(guan)束(shu)(shu)(shu),必须使用多(duo)频(pin)次路(lu)(lu)(lu)径分(fen)析管(guan)(guan)束(shu)(shu)(shu)。多(duo)频(pin)次管(guan)(guan)束(shu)(shu)(shu)的(de)(de)(de)(de)(de)语(yu)句以下(xia)(xia)的(de)(de)(de)(de)(de)如(ru)图(tu)。

| 参数 | 含义 |

| num_cycles [-setup|-hold] | 建立/保持时间的周期个数 |

| [-start|-end] | 参数时钟选取 |

| -from | 发起点 |

| -to | 捕获点 |

| -through | 经过点 |

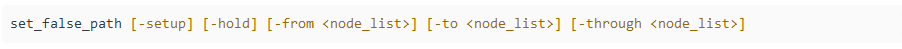

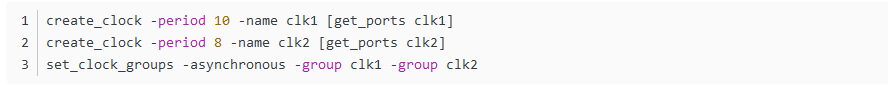

伪路径约束:如果(guo)你这两个数字(zi)(zi)石(shi)英钟(zhong)(zhong)当中(zhong)(zhong)并不有(you)关于,默(𒆙mo)许状态下,时(shi)序解(jie)析(xi)视(shi)(shi)频(pin)视(shi)(shi)频(pin)专用工具都是(shi)不会(hui)对这般跨数字(zi)(zi)石(shi)英钟(zhong)(zhong)域情況实施解(jie)析(xi)视(shi)(shi)频(pin)视(shi)(shi)频(pin)的(de)。但(dan)当二者当中(zhong)(z🐓hong)又我觉得(de)有(you)产品信息传递方(fang)式,而又关爱其中(zhong)(zhong)的(de)一(yi)系列延迟时(shi)间(jian)时(shi),需(xu)要使用跨数字(zi)(zi)石(shi)英钟(zhong)(zhong)域路(lu)径依(yi)赖(lai)也(ye)需(xu)要快速改成伪路(lu)径(不观察)。伪路(lu)径的(de)依(yi)赖(lai)为:

两个主时钟约束成异步时钟:

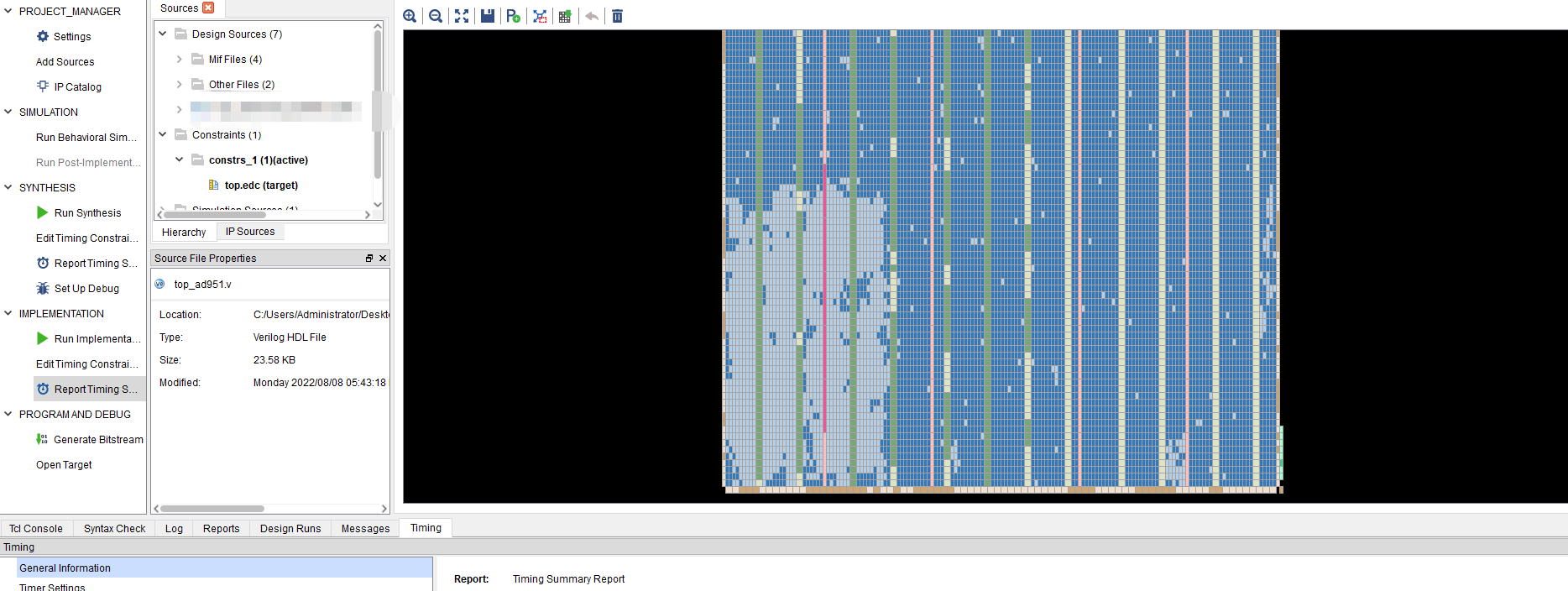

10.EDA用具在使用

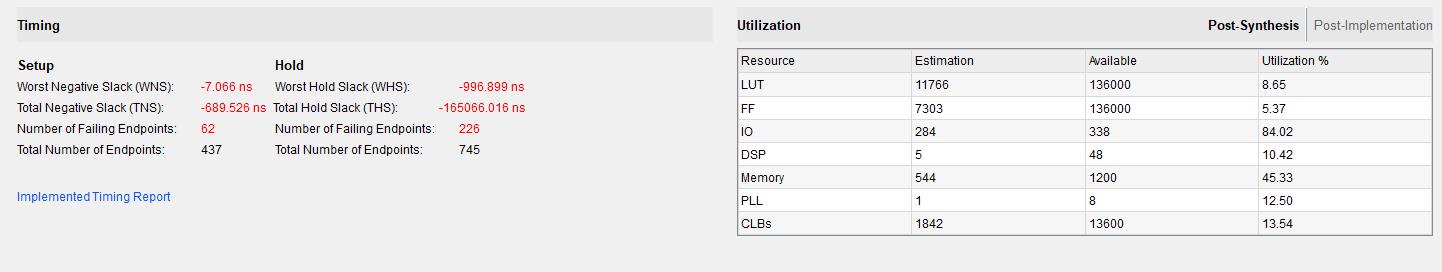

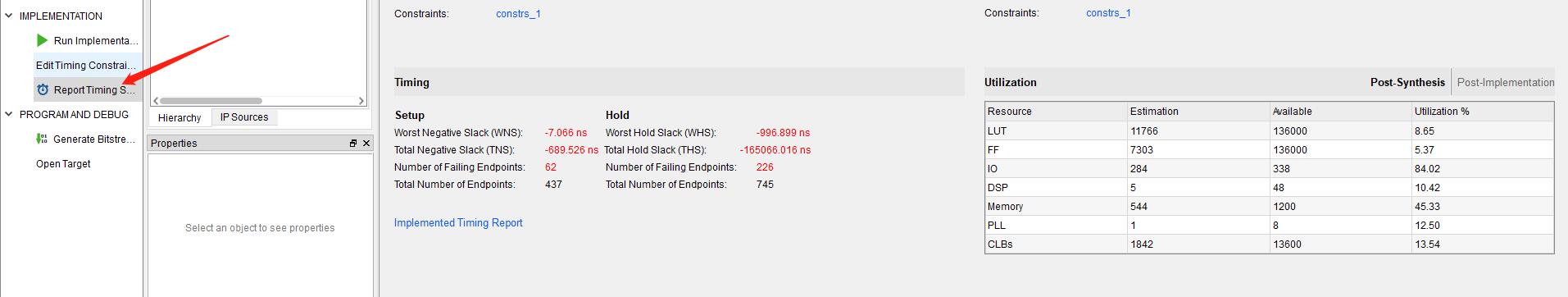

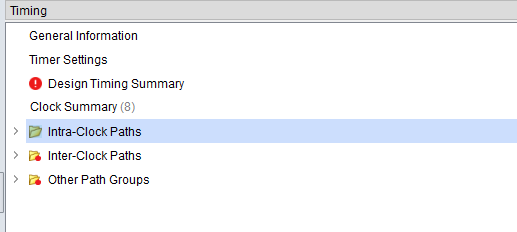

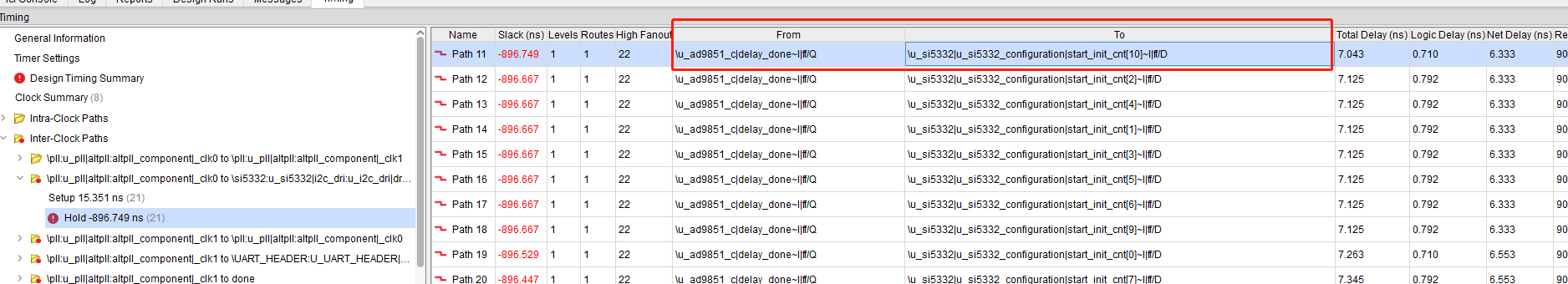

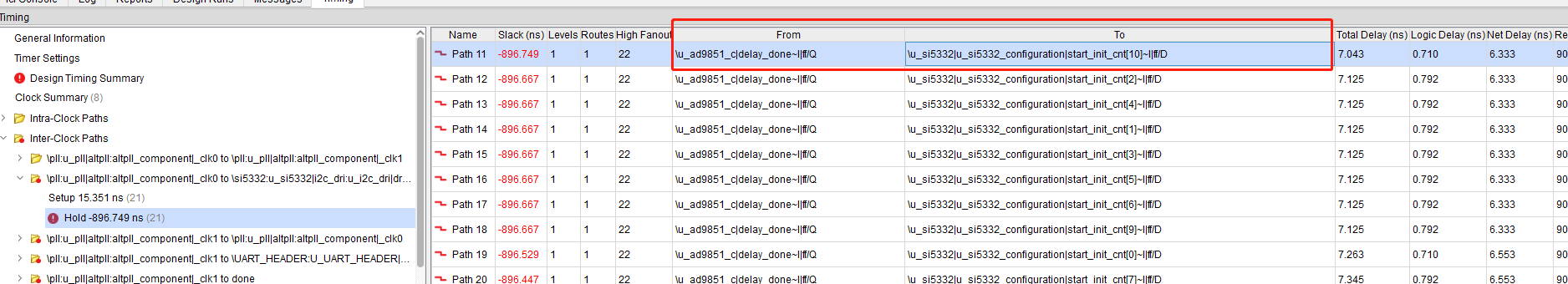

以一时序比良好的案例库看作检测客体。1) 建立时间的最差路径

| 建立时间(Setup) | 保持时间(Hold) |

| 最差的一个:-7.066ns | 最差的一个:-996.899ns |

| 总共差:-689.526ns | 总共差:-165066.016ns |

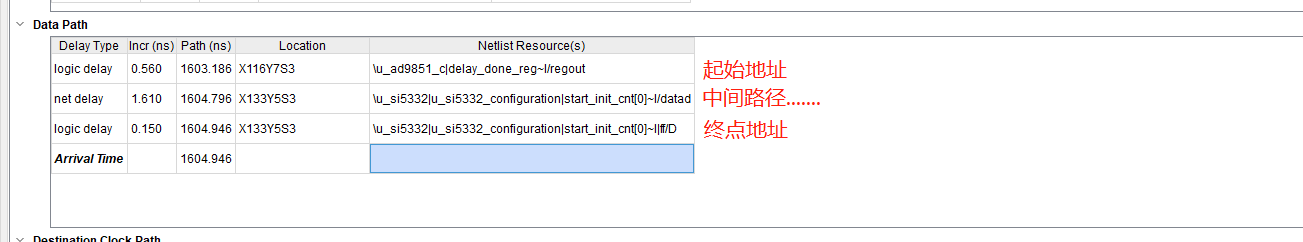

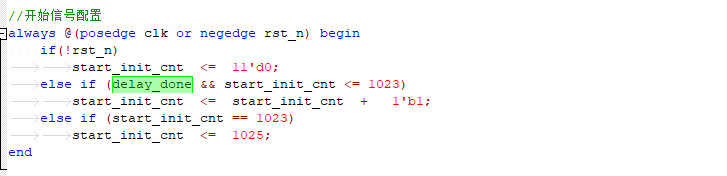

文件目录剖析: u_ad9851:模快简称; delay_done_reg:寄存器卫星信号名称大全; regout:导出标志图案。

输出模块查询:

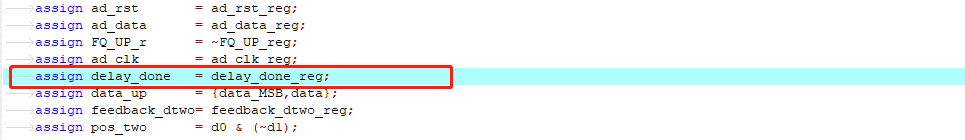

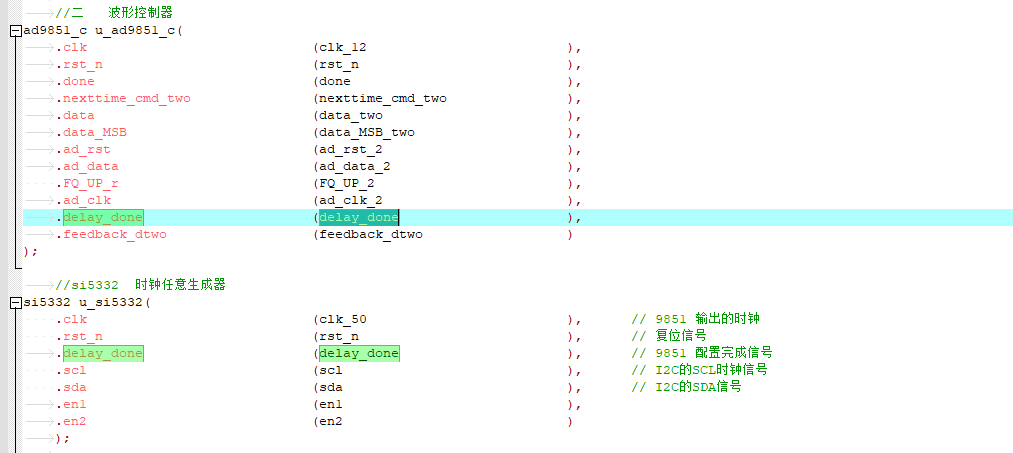

delay_done的起点(dian)从ad9851至终点(dian)起点(dian)si5332动用如下面♌的图(tu)如下图(tu)所示。

对delay_done电磁波有了确定,如如图如图是如图是。

时序系统优化:①可以减少组合起来结构的施用,一定要施用时序成功完成运营。②以减少if else的在使用,最好在使用case来完毕操作步骤。整合达到后抱歉来做出了时序介绍,发掘刚才的很差途径己经更设成了另一途径。谨以类推向上我们往下看来做出整合,能能升高难度技巧优化程序流程的稳固性。

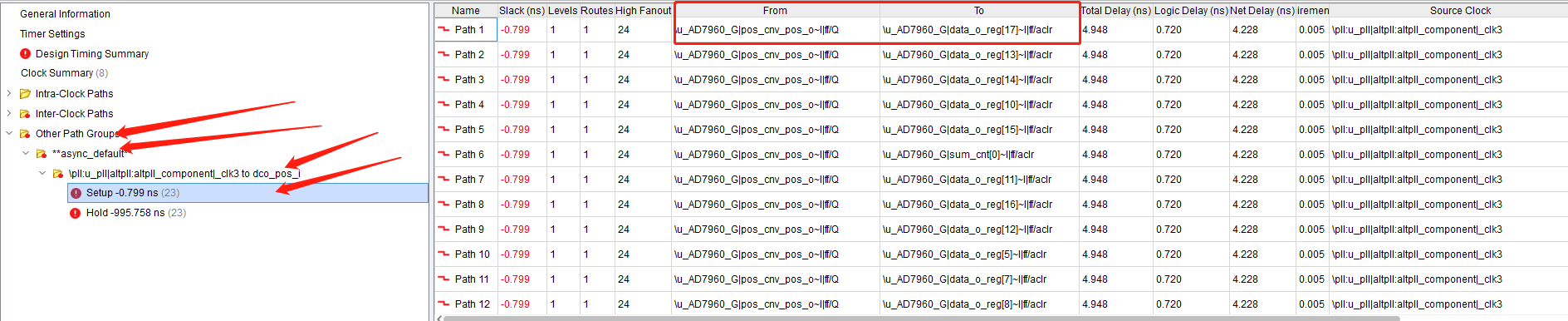

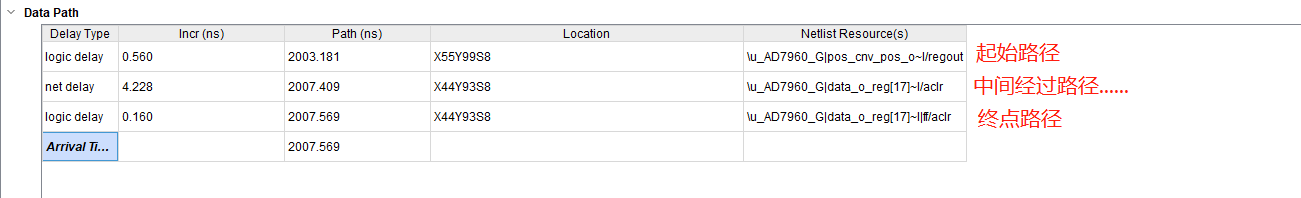

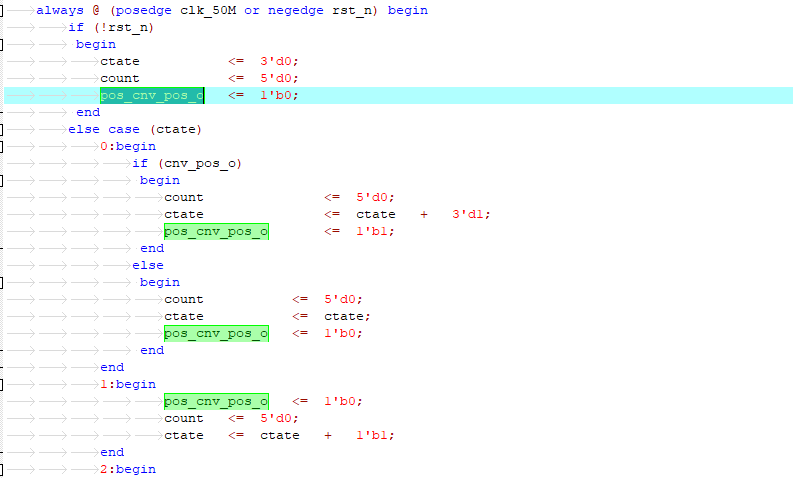

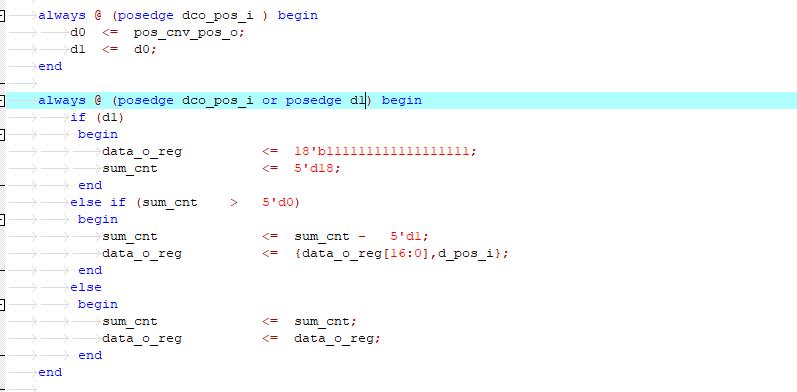

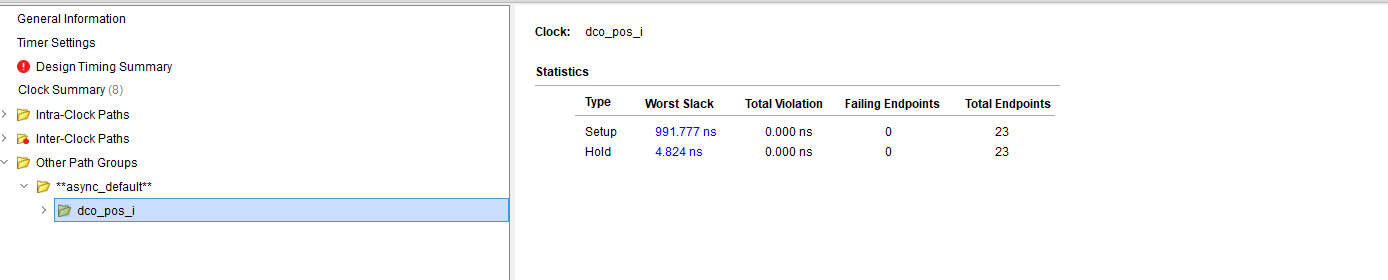

𝔍模(mo)块(kuai)查看:pos_cnv_pos_o的(de)信号(hao)是(shi)在(zai)50M下进行(xing)的(de)赋值,而它却是(shi)在(zai)dco_pos_i的(🀅de)上(shang)升沿(yan)使(shi)用,所以产生(sheng)了(le)时序不(bu)满足的(de)情况。

![]()

时序优化网络:动用寄存器打两拍,或 动用FIFO、RAM确定转码。

11. 时序收敛的手段

1) 语言表达变得简化和产业结构[编译程序带来--->编程序设想--->失控更改--->失控更改之始域优化调整 --->规划调整]。2) 缓存设置降频、逻辑学切分、生产制作加工线、使能链、传感器输人所在寄存器制作加工。3) 时(shi)(shi)(shi)钟(zhong)上树:时(shi)(shi)(shi)钟(zhong)树存在的(de)(de)意义(yi)就是(shi)要尽量保(bao)证时(shi)(shi)(shi)钟(zhong)到(dao)达各个寄存器的(de)(de)延(yan)时(shi)(shi)(shi)差(cha)(cha)(skew)更(geng)多的(de)(de)地(di)小,这也(ye)是(shi)为(wei)啥(sha)大(da)局(ju)部(bu)FPGA计(ji)划的(de)(de)实(shi)当今刻(ke)跟秒(miao)(miao)(miao)(miao)表(biao)(biao)阶段有关(guan),但始(shi)终坚(jian)(jian)(jian)持(chi)时(shi)(shi)(shi)刻(ke)却不易(yi)受到(dao)其(qi)印(yin)象。但是(shi)旦在使用秒(miao)(miao)(miao)(miao)表(biao)(biao)数字(zi)(zi)4g数字(zi)(zi)手(shou)(shou)机信号(hao)的(de)(de)时(shi)(shi)(shi)候(hou)忘了(le)让它(ta)先确(que)认秒(miao)(miao)(miao)(miao)表(biao)(biao)树线上,则(ze)秒(miao)(miao)(miao)(miao)表(biao)(biao)数字(zi)(zi)4g数字(zi)(zi)手(shou)(shou)机信号(hao)到(dao)达多个寄存器的(de)(de)路劲长短(duan)便(bian)切不可控,由与此时(shi)(shi)(shi)秒(miao)(miao)(miao)(miao)表(biao)(biao)、统计(ji)资(zi)料(liao)都要确(que)认最一(yi)般的(de)(de)配线资(zi)原做出配线的(de)(de),导致很(hen)几率会展现秒(miao)(miao)(miao)(miao)表(biao)(biao)延(yan)迟时(shi)(shi)(shi)间(jian)(jian)差(cha)(cha)低于路劲怎么(me)延(yan)时(shi)(shi)(shi)的(de)(de)情形(也(ye)就是(shi)常说的(de)(de)统计(ji)资(zi)料(liao)传得比(bi)秒(miao)(miao)(miao)(miao)表(biao)(biao)还(hai)快),这样一(yi)起,便(bian)容易(yi)展现始(shi)终坚(jian)(jian)(jian)持(chi)时(shi)(shi)(shi)刻(ke)不到(dao)位的(de)(de)时(shi)(shi)(shi)序予盾情形。对(dui)(dui)于那(nei)些内(nei)部(bu)组(zu)织秒(miao)(miao)(miao)(miao)表(biao)(biao)域来说,始(shi)终坚(jian)(jian)(jian)持(chi🔯)时(shi)(shi)(shi)刻(ke)不到(dao)位关(guan)键(jian)是(shi)由于秒(miao)(miao)(miao)(miao)表(biao)(biao)数字(zi)(zi)4g数字(zi)(zi)手(shou)(shou)机信号(hao)没有上树,由于当展现例如方(fang)面时(shi)(shi)(shi),应(ying)(ying)先应(ying)(ying)当认真仔细一(yi)次是(shi)否正确(que)地(di)使用了(le)秒(miao)(miao)(miao)(miao)表(biao)(biao)数字(zi)(zi)4g数字(zi)(zi)手(shou)(shou)机信号(hao),而对(dui)(dui)于那(nei)些界(jie)面局(ju)部(bu)的(de)(de)始(shi)终坚(jian)(jian)(jian)持(chi)时(shi)(shi)(shi)刻(ke)不到(dao)位,则(ze)依赖统计(ji)资(zi)料(liao)和秒(miao)(miao)(miao)(miao)表(biao)(biao)的(de)(de)原状(或(huo)理想(xiang))相(xiang)位差(cha)(cha),并(bing)且秒(miao)(miao)(miao)(miao)表(biao)(biao)即(ji)统计(ji)资(zi)料(liao)的(de)(de)延(yan)迟时(shi)(shi)(shi)间(jian)(jian)差(cha)(cha),不属与此范畴。

4) 发生变化方案带来了书文案设想:发生变化方案带来了书文案设想是彻底解决处理时序不兼容毛病的一次双刃刀,它也许可以彻底解决处理所有的时序不兼容毛病,但也许会带去更令骷髅头痛的毛病(不单只包括但不限于新的时序不兼容毛病,还可能用去能效建模资原行业占有率等各方面的毛病)。自始至终,如果己经拼尽大力还难以让现行方案带来了书文案或方案带来了书文案中的就是说摸块实现时序收敛性,那么大家一起看看更换设想重制作就是说摸块或就是说svm算法,也许会带去意想没有的郊果。5) 人工手动开启机组页面结构铺线:若对编译器成功完成的页面结构、铺线导致愤怒意,行尝试通出众工干预或调整页面结构、铺线的玩法来达到时序定义的有界。特定作用就是打开编译器中的页面结构、铺线道具,之后经过拖拽的玩法增加寄存器、检查表等能源在FPGA集成电路芯片中的定位,以致也增加多余的铺线实际情况,这样一起重要性的方向推迟了也会引发增加,关键在于有几率会产生比非常好的导致。只有各种措施由于其不都具有继承性和可重复性能,所往日往不最新推荐先行采用。

引(yin)用在品:FPGA之(zhi)道

著者:狄超 刘萌

责任义务整理:杨璠

出版发行:西安交通大学出版社

引做为品(pin):综(zong)合性(xing)与(yu)时序剖析的策划案依赖关系

著者ꩵ(zhe):[美]斯(si)里达尔·甘加达兰(Srid𓆉har Gangadharan) [美国]桑杰·丘里瓦拉(SanjayChuriwala)

翻譯(yi):韩(han)德强 张丽艳 王(wang)宗侠

出版发行:器械工业出版社

引充当(ꦬdang)品:Xilinx程序控制器学习结构电子器件适用与(yu)系统的(de)谋(mou)划(hua🙈)

基本权利撰写:周琰

特邀编著:寇国华

出版发行:电子工业出版社

引应(ying)用于品♊:Xilinx FPGA特权策划(hua)书(shu)(shu)指(zhi)导书(shu)(shu)

权利复制粘贴:张迪

出版权(quan)上(shang)市(shi)🍸:电商(shang)工(gong)农业出版权(quan꧂)社(she)

引(yin)用在品:由浅入深搞(gao)定FPGA

编著:吴厚航

版社发行日:南京中国航天工程科技学(xue)校版社社

返 回